# **Hardware Watermarking of Transient Fault Detectable IP Designs using Multivariate Encoded HLS Scheduling based Multi Modal Security Methodology**

**Published in IET-CDT**

Anirban Sengupta, Vishal Chourasia, Nabendu Bhui, Aditya Anshul, “Watermarking of Transient Fault-Detectable IP Designs Using Multivariate HLS Scheduling Based Multimodal Security:”, *IET Computers & Digital Techniques*, 2025, 5926846, 17 pages, 2025.

# Introduction

- The Modern computing system development relies on collaboration with multiple third-party IP vendors, creating potential security risks.

- This growing threat highlights the urgent need for robust security measures to protect hardware IP cores from misuse and abuse [1].

- However besides robust security countermeasure as the need of the hour, there is also a growing need to design IP cores that are fault secure (detectable) or fault tolerant due to potential transient fault that may occur.

[1] H. Pearce, R. Karri, B. Tan. 2023. High-Level Approaches to Hardware Security: A Tutorial. ACM Trans. Embed. Compu. Syst. 22, 3, Article 45, May 2023..

# Novel Contributions of the Paper

- Presents a hardware watermarking methodology for transient fault-detectable IP designs.

- Presents a hardware watermarking methodology that leverages multivariate encoded HLS scheduling based multi-modal security.

- The presented IP watermarking technique is more robust than the prior watermarking techniques in terms of probability of coincidence, tamper tolerance, and probability of watermark decoding attack.

# Related Work

| Sr. No. | Existing Work                   | Technique Used                                 | Remark                                                                                                   |

|---------|---------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 1.      | S. Rai, et.al., [21] (2019)     | polymorphic inverter designs                   | However, [21],[22] produces watermark IP designs vulnerable to watermark collision and tampering attacks |

| 2.      | R. Karmakar, et.al.,[22] (2022) | sequential circuits using finite state machine |                                                                                                          |

| 3.      | A. Sengupta et.al., [6] (2019)  | hardware steganography-based security          | However, bypass the piracy detection system by replicating the stego-mark                                |

[21] S. Rai, A. Rupani, P. Nath and A. Kumar, "Hardware Watermarking Using Polymorphic Inverter Designs Based On Reconfigurable Nanotechnologies," *2019 IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, 2019, pp. 663-669..

[22] R. Karmakar, S. S. Jana and S. Chattopadhyay, "A Cellular Automata Guided Finite-State-Machine Watermarking Strategy for IP Protection of Sequential Circuits," *IEEE Trans. Emerg. Topics Comput.*, vol. 10, no. 2, pp. 806-823, 1 April-June 2022..

[6]. A. Sengupta, M. Rathor "IP Core Steganography for Protecting DSP Kernels used in CE Systems", *IEEE Trans. on Consumer Electronics*, Vol: 65, Issue: 4, pp. 506 – 515, Nov. 2019.

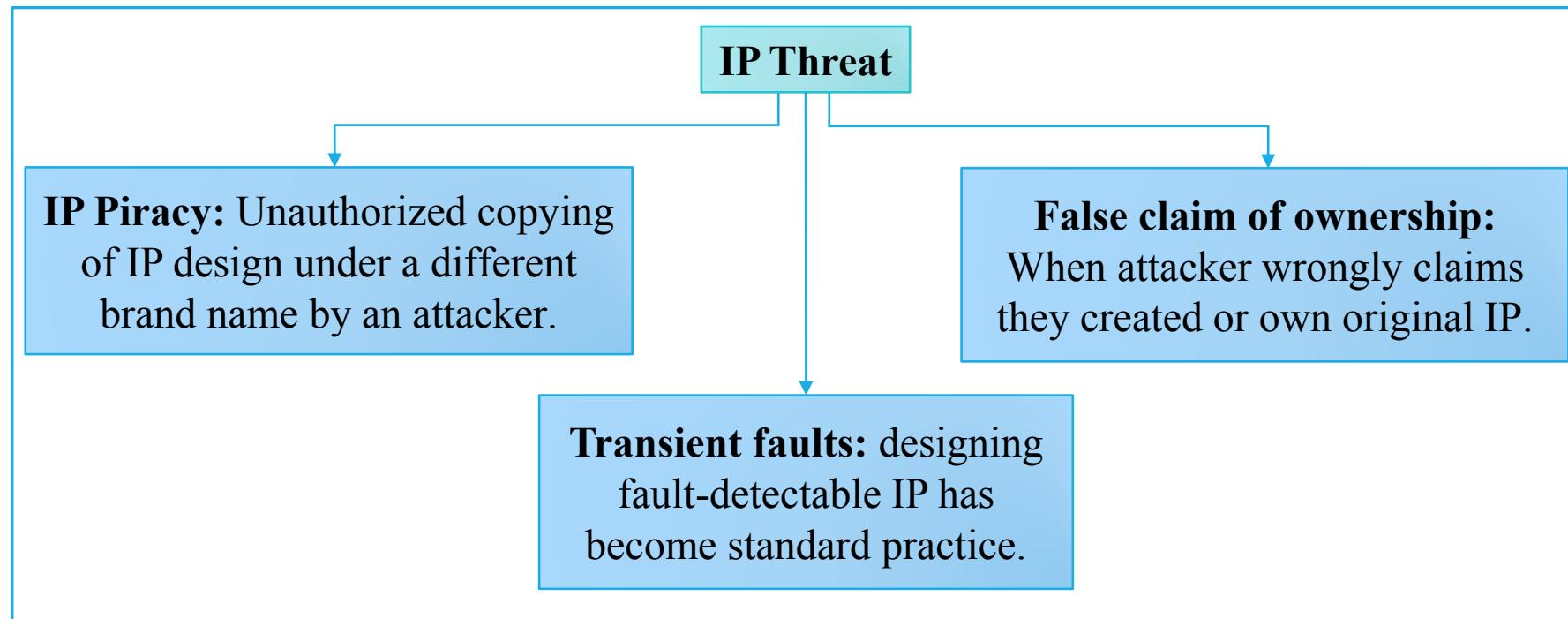

# Threat Model

- [5]. D. Karaklajić, J. -M. Schmidt and I. Verbauwhede, "Hardware Designer's Guide to Fault Attacks," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 21, no. 12, pp. 2295-2306, Dec. 2013.

- [6] A. Sengupta, M. Rathor "IP Core Steganography for Protecting DSP Kernels used in CE Systems", *IEEE Trans. on Consumer Electronics*, Vol: 65, Issue: 4, pp. 506 – 515, Nov. 2019.

- [7] M. Rostami, F. Koushanfar and R. Karri, "A Primer on Hardware Security: Models, Methods, and Metrics," *Proceedings of the IEEE*, vol. 102, no. 8, pp. 1283-1295, Aug. 2014

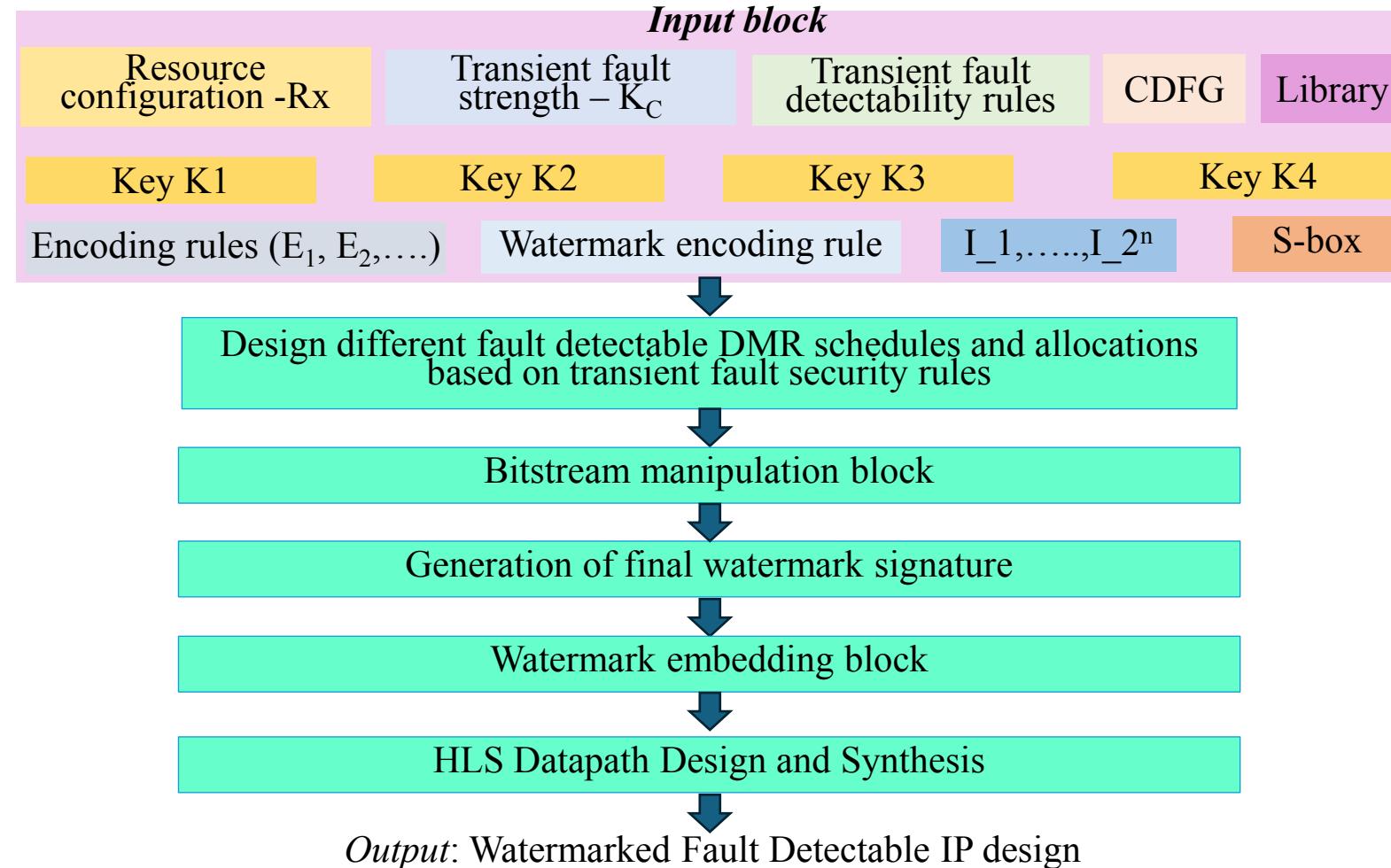

# Proposed Methodology: Overview

Fig. 1. Overview of the proposed approach

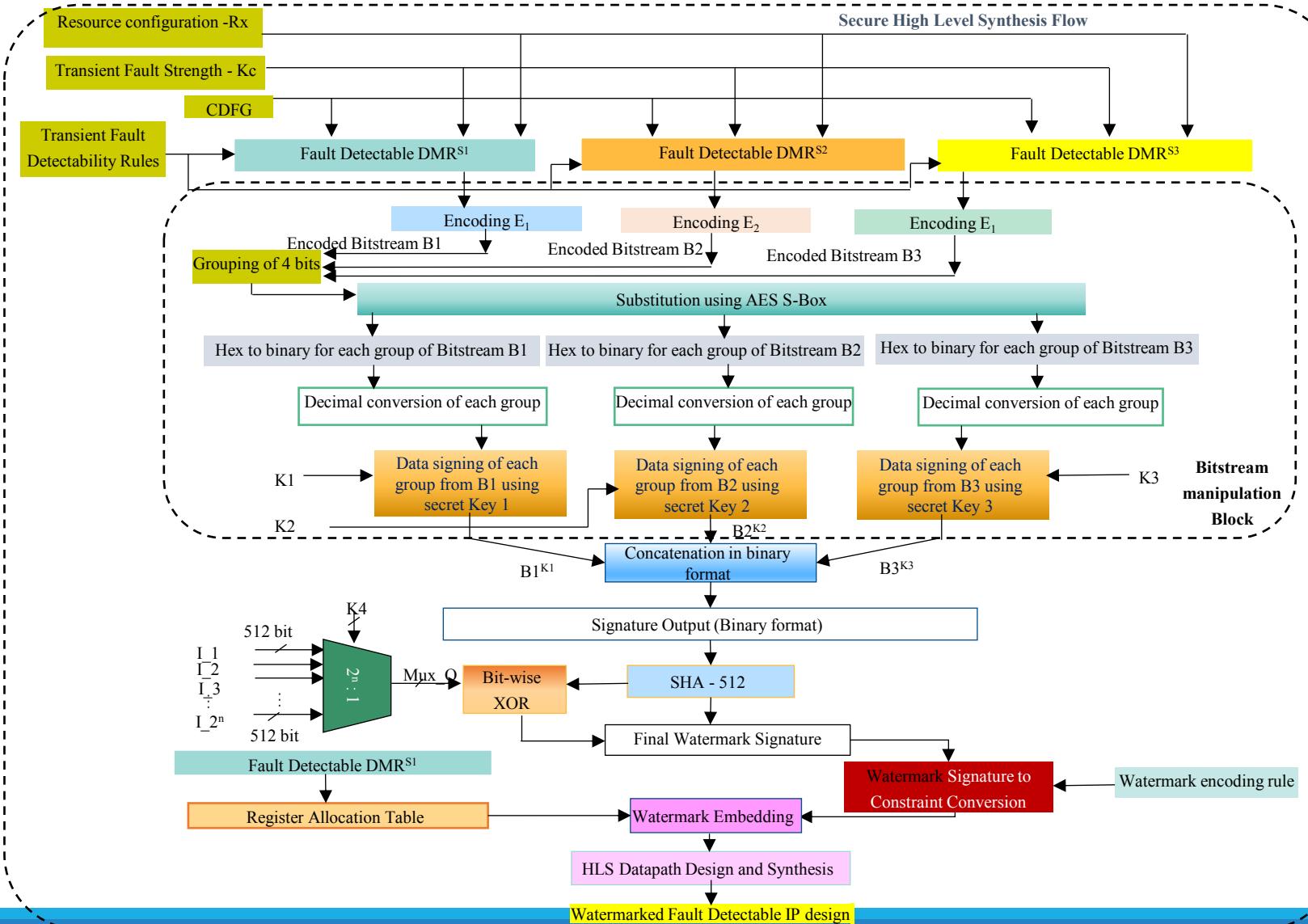

# Details of Proposed Methodology

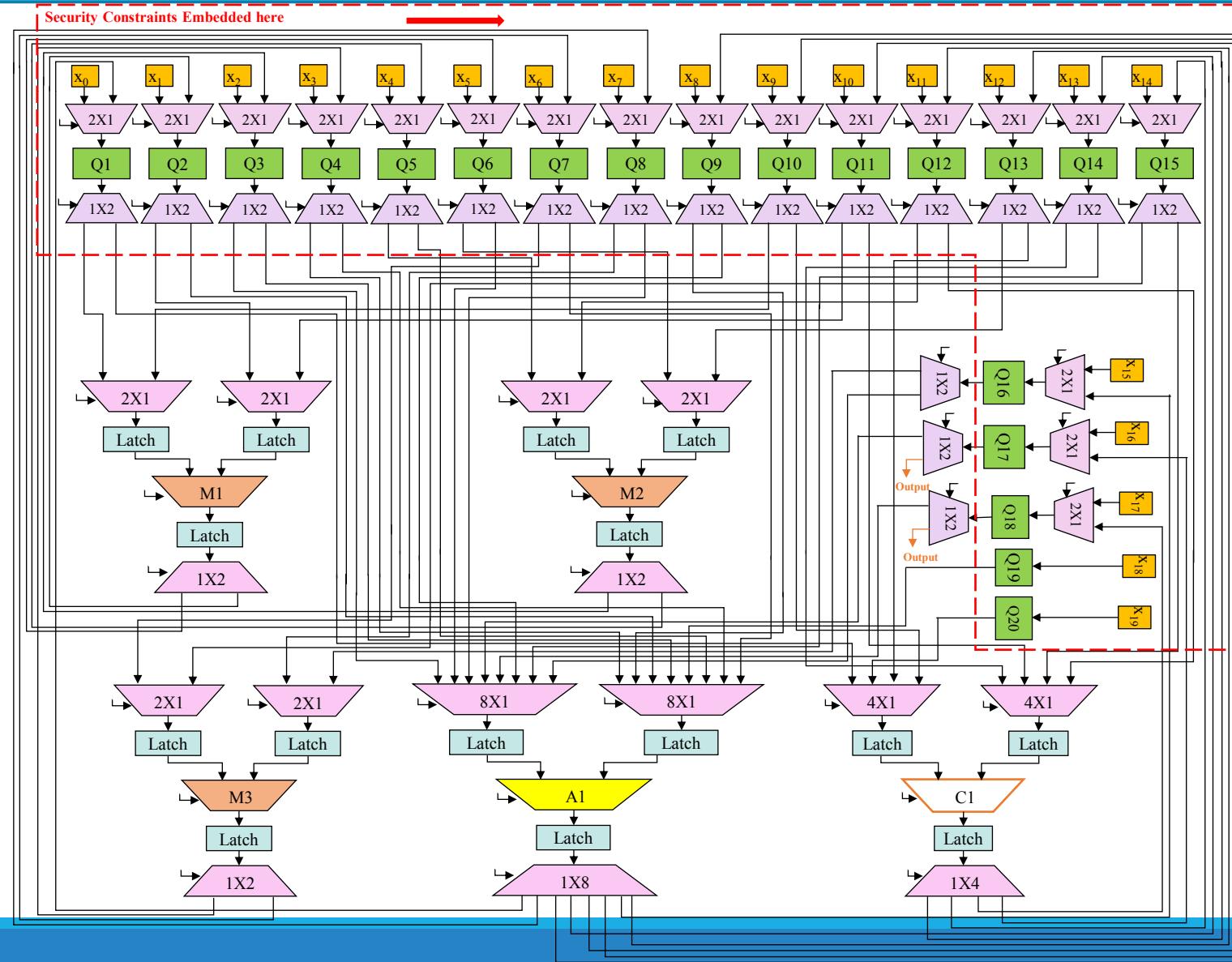

Fig. 2(a). Details of the proposed hardware IP watermarking approach

# Details of Proposed Methodology

**Pseudocode:** Algorithm to implement  $2^n:1$  Mux switch

**Input:**  $I_1, I_2, \dots, I_{2^n}$  (each 512-bits wide) and  $K4$ .

**Output:**  $Mux\_O$  acting as input to the XOR operation.

```

IF ( $K4 == "0000.....00000"$ ) // size of  $K4$  is n-bit

$Mux\_O \leftarrow I_1$

```

END IF

EXIT

```

IF ( $K4 == "0000.....00001"$ ) // size of  $K4$  is n-bit

$Mux\_O \leftarrow I_2$

```

END IF

EXIT

```

IF ( $K4 == "0000.....00010"$ ) // size of  $K4$  is n-bit

$Mux\_O \leftarrow I_3$

```

END IF

EXIT

⋮

```

IF ( $K4 == "1111.....11111"$ ) // size of  $K4$  is n-bit

$Mux\_O \leftarrow I_{2^n}$

```

END IF

EXIT

ELSE

$Mux\_O \leftarrow Z$  //  $Z$  indicates high impedance state

END IF

EXIT

Fig.2(b). Pseudocode to implement  $2^n:1$  Mux switch

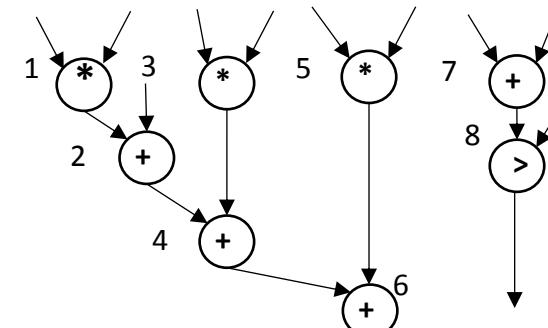

Fig. 3. Data flow graph of FIR filter (UF=3)

# Generation of Fault Detectable Scheduled Design

## Transient Fault-Detectability Rules

1. If original and sister operations of respective original and duplicate units are *KC-control step* apart, then allocate the same hardware resource (*i.e.*, multiplier, adder, or subtractor) in the sister operations accordingly.

2. If there is availability of multiple hardware instances of the same type, then allocate distinct hardware resources in the sister operation of the DMR to ensure fault detection.

3. If the above rules do not ensure fault detectability, then reschedule the sister operations of the duplicate unit by shifting downward, one control step at a time, until it complies with the first rule.

# Generation of Fault Detectable Scheduled Design

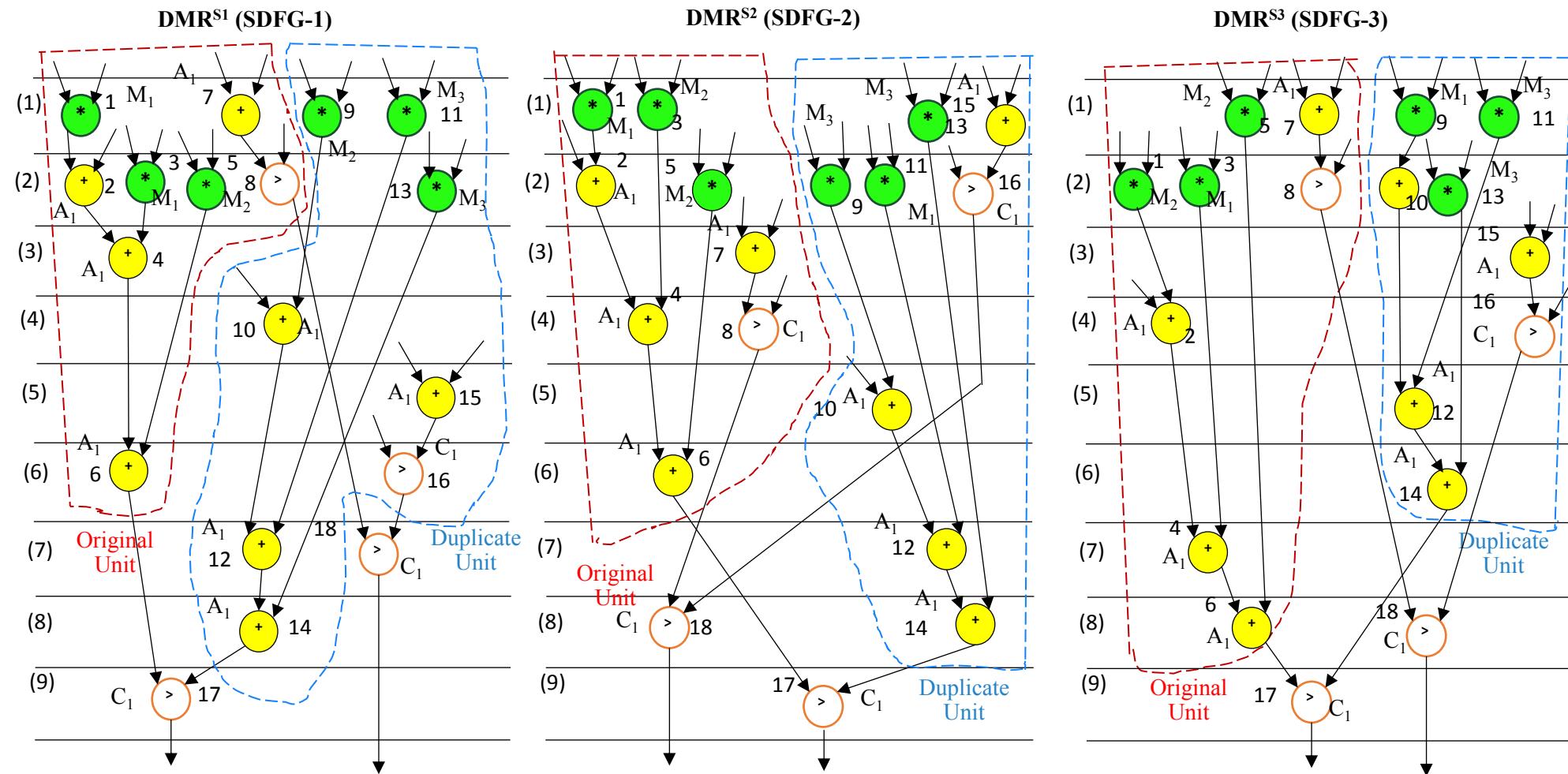

Fig.4. (a). Generation of different scheduled fault detectable FIR filter (UF=3).

# Generation of Encoded Bitstream

Fig. 4(b). Generation of encoded bitstream (B1, B2, and B3)

# Generation of Final Watermark signature

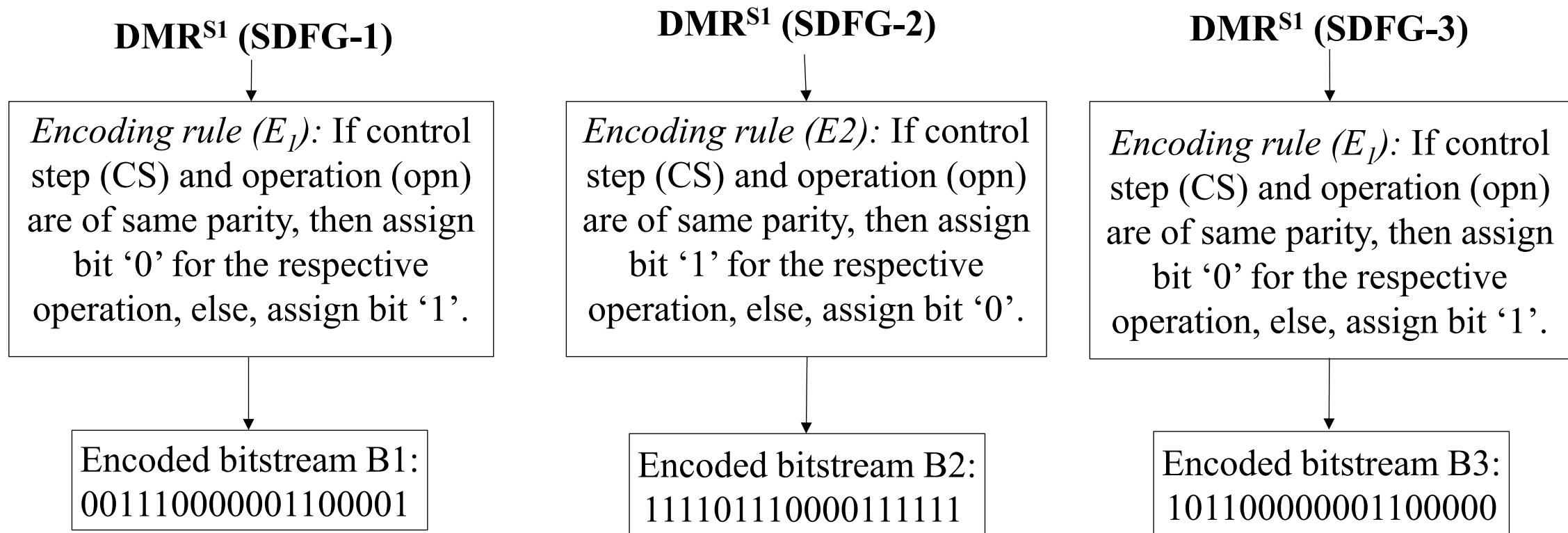

Fig. 5. Demonstration of final watermark signature generation using proposed approach (for FIR filter)

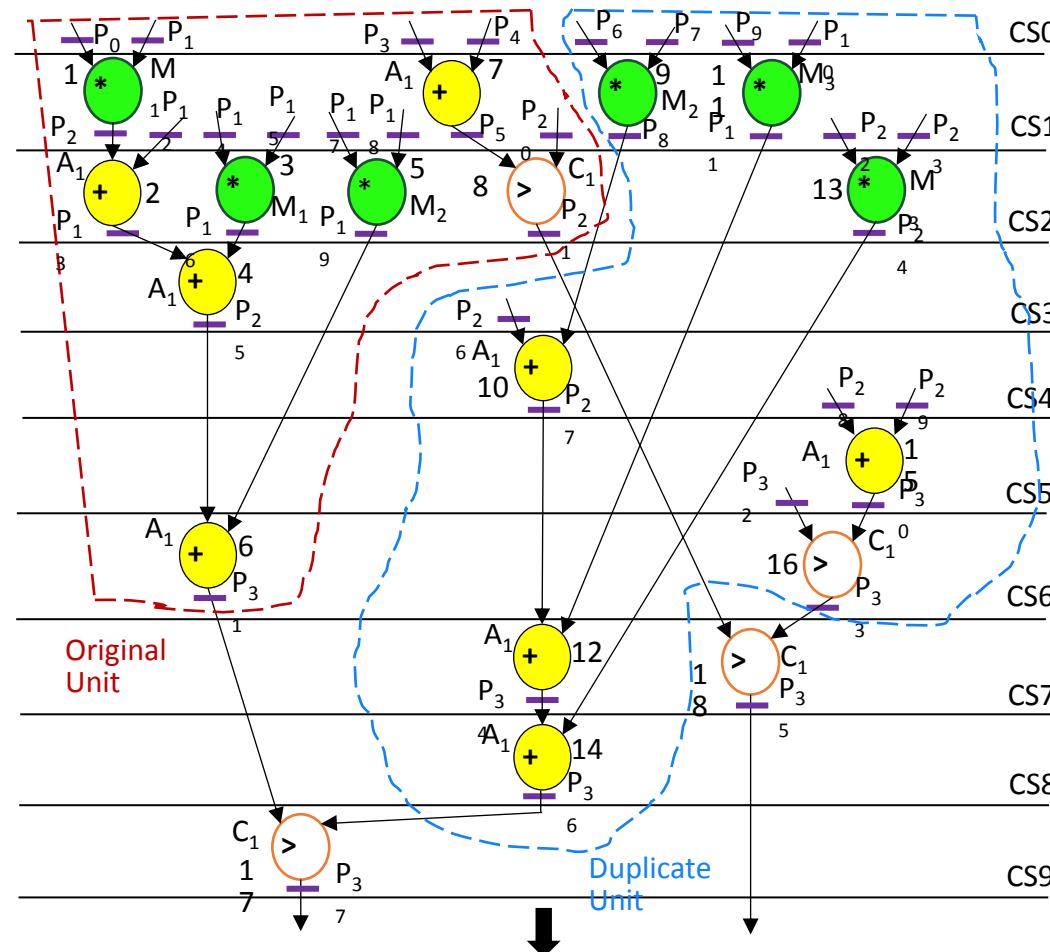

# Watermark Embedding Rule

## Embedding rule:

1. If the watermark signature bit is 0, then even-even storage variable pairs  $(P_i, P_j)$  from the fault detectable DMR design are generated as watermark constraints, where  $i$  and  $j$  represent the storage variable indices.

2. If the watermark signature bit 1, the generated watermark constraints are odd-odd storage variable pairs of the fault detectable DMR design.

# Watermark Embedding Process

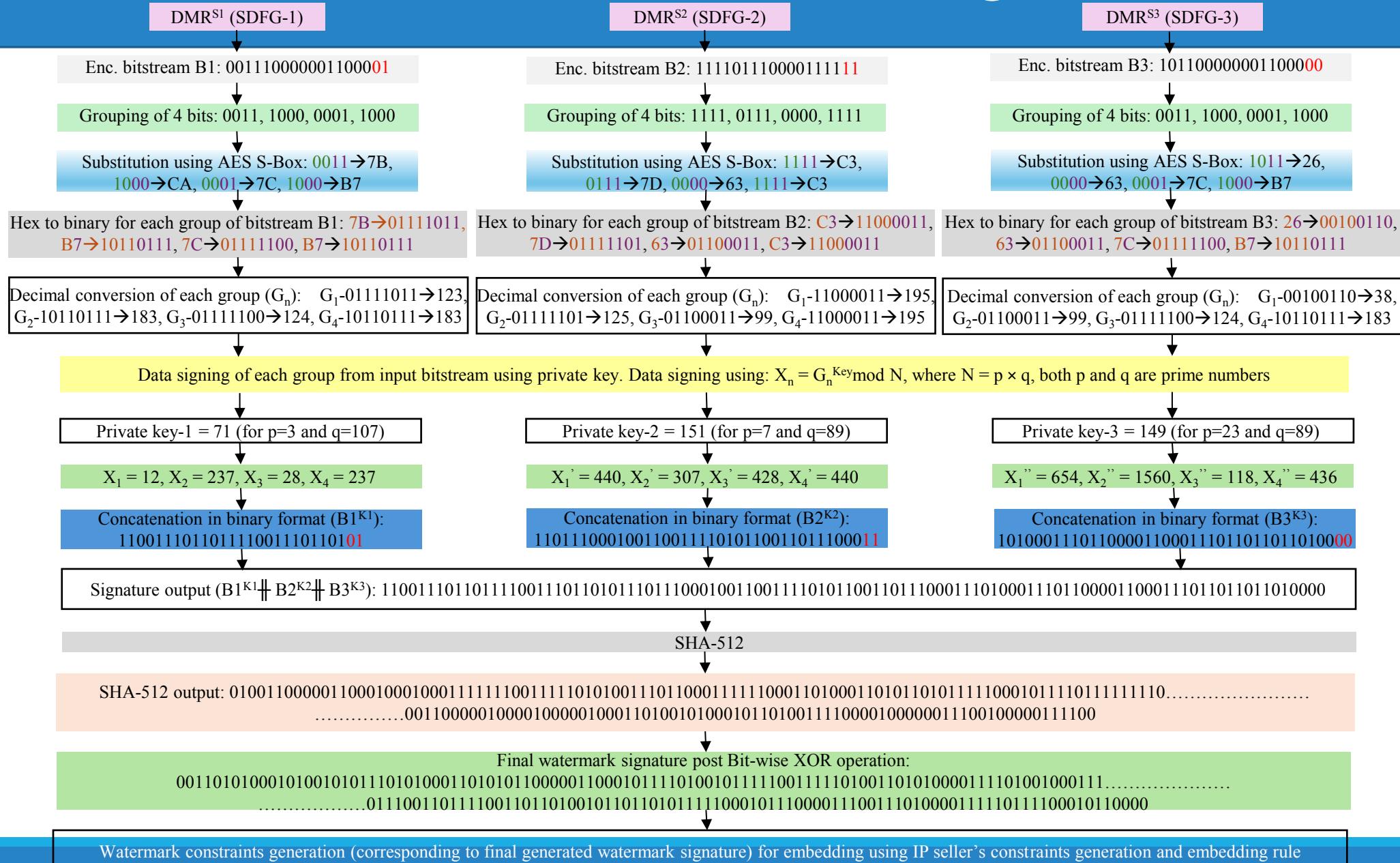

Fig. 6. Fault schedule DMR SDFG of FIR filter (UF=3, using Rx = 1 adder (+), 3 multiplier (\*), 1 comparator (>), and Kc = 2CS) and its corresponding RAT (pre-embedding)

Pre-embedding Register allocation table of Fault Secured FIR (UF=3)

| Control Step | CS0      | CS1      | CS2      | CS3      | CS4      | CS5      | CS6      | CS7      | CS8      | CS9      |

|--------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| <b>Q1</b>    | $P_0$    | $P_2$    | $P_{13}$ | $P_{25}$ | $P_{25}$ | $P_{25}$ | $P_{31}$ | $P_{31}$ | $P_{31}$ | $P_{37}$ |

| <b>Q2</b>    | $P_1$    | $P_5$    | $P_{16}$ | -        | $P_{27}$ | $P_{27}$ | $P_{27}$ | $P_{34}$ | $P_{36}$ | -        |

| <b>Q3</b>    | $P_3$    | $P_8$    | $P_8$    | $P_8$    | -        | $P_{38}$ | $P_{33}$ | $P_{35}$ | $P_{35}$ | $P_{35}$ |

| <b>Q4</b>    | $P_4$    | $P_{11}$ | $P_{11}$ | $P_{11}$ | $P_{11}$ | $P_{11}$ | $P_{11}$ | -        | -        | -        |

| <b>Q5</b>    | $P_6$    | -        | $P_{19}$ | $P_{19}$ | $P_{19}$ | $P_{19}$ | -        | -        | -        | -        |

| <b>Q6</b>    | $P_7$    | -        | $P_{21}$ | $P_{21}$ | $P_{21}$ | $P_{21}$ | $P_{21}$ | -        | -        | -        |

| <b>Q7</b>    | $P_9$    | -        | $P_{24}$ | $P_{24}$ | $P_{24}$ | $P_{24}$ | $P_{24}$ | $P_{24}$ | -        | -        |

| <b>Q8</b>    | $P_{10}$ | -        | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q9</b>    | $P_{12}$ | $P_{12}$ | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q10</b>   | $P_{14}$ | $P_{14}$ | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q11</b>   | $P_{15}$ | $P_{15}$ | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q12</b>   | $P_{17}$ | $P_{17}$ | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q13</b>   | $P_{18}$ | $P_{18}$ | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q14</b>   | $P_{20}$ | $P_{20}$ | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q15</b>   | $P_{22}$ | $P_{22}$ | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q16</b>   | $P_{23}$ | $P_{23}$ | -        | -        | -        | -        | -        | -        | -        | -        |

| <b>Q17</b>   | $P_{26}$ | $P_{26}$ | $P_{26}$ | -        | -        | -        | -        | -        | -        | -        |

| <b>Q18</b>   | $P_{28}$ | $P_{28}$ | $P_{28}$ | $P_{28}$ | -        | -        | -        | -        | -        | -        |

| <b>Q19</b>   | $P_{29}$ | $P_{29}$ | $P_{29}$ | $P_{29}$ | -        | -        | -        | -        | -        | -        |

| <b>Q20</b>   | $P_{32}$ | -        | -        | -        |

# Watermark Embedding Process

**Table I**

**Post Embedding Register allocation table of Fault Secured FIR (UF=3)**

| Control Steps<br>(CS0-CS9)/<br>Registers (Q1-<br>Q20) | CS0                   | CS1                                | CS2                   | CS3                   | CS4                   | CS5                   | CS6                   | CS7                   | CS8                   | CS9                   |

|-------------------------------------------------------|-----------------------|------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| <b>Q1</b>                                             | <b>P<sub>0</sub></b>  | <b>P<sub>2</sub>/P<sub>5</sub></b> | <b>P<sub>13</sub></b> | <b>P<sub>25</sub></b> | <b>P<sub>25</sub></b> | <b>P<sub>25</sub></b> | <b>P<sub>31</sub></b> | <b>P<sub>31</sub></b> | <b>P<sub>31</sub></b> | <b>P<sub>37</sub></b> |

| <b>Q2</b>                                             | <b>P<sub>1</sub></b>  | <b>P<sub>5</sub></b>               | <b>P<sub>16</sub></b> | —                     | <b>P<sub>27</sub></b> | <b>P<sub>27</sub></b> | <b>P<sub>27</sub></b> | <b>P<sub>34</sub></b> | <b>P<sub>36</sub></b> | —                     |

| <b>Q3</b>                                             | <b>P<sub>3</sub></b>  | <b>P<sub>8</sub></b>               | <b>P<sub>8</sub></b>  | <b>P<sub>8</sub></b>  | —                     | <b>P<sub>30</sub></b> | <b>P<sub>33</sub></b> | <b>P<sub>35</sub></b> | <b>P<sub>35</sub></b> | <b>P<sub>35</sub></b> |

| <b>Q4</b>                                             | <b>P<sub>4</sub></b>  | <b>P<sub>11</sub></b>              | <b>P<sub>11</sub></b> | <b>P<sub>11</sub></b> | <b>P<sub>11</sub></b> | <b>P<sub>11</sub></b> | <b>P<sub>11</sub></b> | —                     | —                     | —                     |

| <b>Q5</b>                                             | <b>P<sub>6</sub></b>  | —                                  | <b>P<sub>19</sub></b> | <b>P<sub>19</sub></b> | <b>P<sub>19</sub></b> | <b>P<sub>19</sub></b> | —                     | —                     | —                     | —                     |

| <b>Q6</b>                                             | <b>P<sub>7</sub></b>  | <b>P<sub>2</sub></b>               | <b>P<sub>21</sub></b> | <b>P<sub>21</sub></b> | <b>P<sub>21</sub></b> | <b>P<sub>21</sub></b> | <b>P<sub>21</sub></b> | —                     | —                     | —                     |

| <b>Q7</b>                                             | <b>P<sub>9</sub></b>  | —                                  | <b>P<sub>24</sub></b> | <b>P<sub>24</sub></b> | <b>P<sub>24</sub></b> | <b>P<sub>24</sub></b> | <b>P<sub>24</sub></b> | <b>P<sub>24</sub></b> | —                     | —                     |

| <b>Q8</b>                                             | <b>P<sub>10</sub></b> | —                                  | <b>P<sub>13</sub></b> | —                     | —                     | —                     | —                     | —                     | —                     | —                     |

| <b>Q9</b>                                             | <b>P<sub>12</sub></b> | <b>P<sub>12</sub></b>              | —                     | <b>P<sub>25</sub></b> | <b>P<sub>25</sub></b> | <b>P<sub>25</sub></b> | —                     | —                     | —                     | —                     |

| <b>Q10</b>                                            | <b>P<sub>14</sub></b> | <b>P<sub>14</sub></b>              | —                     | —                     | —                     | —                     | <b>P<sub>31</sub></b> | <b>P<sub>31</sub></b> | <b>P<sub>31</sub></b> | —                     |

| <b>Q11</b>                                            | <b>P<sub>15</sub></b> | <b>P<sub>15</sub></b>              | —                     | —                     | —                     | <b>P<sub>30</sub></b> | —                     | —                     | —                     | —                     |

| <b>Q12</b>                                            | <b>P<sub>17</sub></b> | <b>P<sub>17</sub></b>              | —                     | —                     | —                     | —                     | —                     | —                     | <b>P<sub>36</sub></b> | —                     |

| <b>Q13</b>                                            | <b>P<sub>18</sub></b> | <b>P<sub>18</sub></b>              | <b>P<sub>21</sub></b> | <b>P<sub>21</sub></b> | <b>P<sub>21</sub></b> | <b>P<sub>21</sub></b> | <b>P<sub>21</sub></b> | —                     | —                     | —                     |

| <b>Q14</b>                                            | <b>P<sub>20</sub></b> | <b>P<sub>20</sub></b>              | —                     | —                     | <b>P<sub>27</sub></b> | <b>P<sub>27</sub></b> | <b>P<sub>27</sub></b> | —                     | —                     | —                     |

| <b>Q15</b>                                            | <b>P<sub>22</sub></b> | <b>P<sub>22</sub></b>              | —                     | —                     | —                     | —                     | <b>P<sub>33</sub></b> | —                     | —                     | —                     |

| <b>Q16</b>                                            | <b>P<sub>23</sub></b> | <b>P<sub>23</sub></b>              | —                     | —                     | —                     | —                     | —                     | <b>P<sub>34</sub></b> | —                     | —                     |

| <b>Q17</b>                                            | <b>P<sub>26</sub></b> | <b>P<sub>26</sub></b>              | <b>P<sub>26</sub></b> | —                     | —                     | —                     | —                     | —                     | <b>P<sub>37</sub></b> | —                     |

| <b>Q18</b>                                            | <b>P<sub>28</sub></b> | <b>P<sub>28</sub></b>              | <b>P<sub>28</sub></b> | <b>P<sub>28</sub></b> | —                     | —                     | —                     | <b>P<sub>35</sub></b> | <b>P<sub>35</sub></b> | <b>P<sub>35</sub></b> |

| <b>Q19</b>                                            | <b>P<sub>29</sub></b> | <b>P<sub>29</sub></b>              | <b>P<sub>29</sub></b> | <b>P<sub>29</sub></b> | —                     | —                     | —                     | —                     | —                     | —                     |

| <b>Q20</b>                                            | <b>P<sub>32</sub></b> | <b>P<sub>32</sub></b>              | <b>P<sub>32</sub></b> | <b>P<sub>32</sub></b> | <b>P<sub>32</sub></b> | <b>P<sub>32</sub></b> | —                     | —                     | —                     | —                     |

# Watermark Embedding Process

# Watermark Detection/ Validation

- An attacker needs to decode several security layers and parameters used for watermark signature generation, in order to establish the watermark:

- i. Multivariate fault detectable DMR design and their corresponding encoded bitstream generation process using encoding keys E1, E2..., En.

- ii. Employed AES S-box and data signing keys K1, K2, and K3.

- iii. Concatenation rule to generate the binary signature output.

- iv. SHA-512 and 2n:1 Mux-controlled bit-wise XOR operation.

- v. Encoding rule used for watermark constraint generation and embedding.

These parameters are unknown to an attacker. Thus, the proposed approach provides more definite proof-of-IP authenticity.

# Results and Analysis

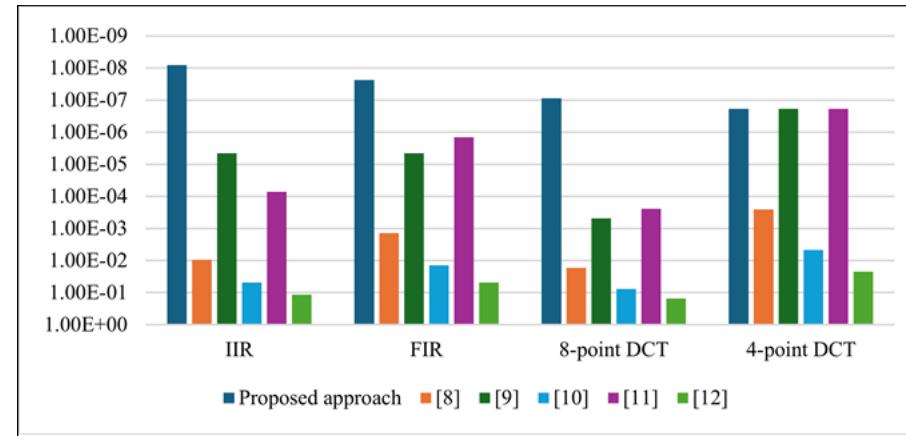

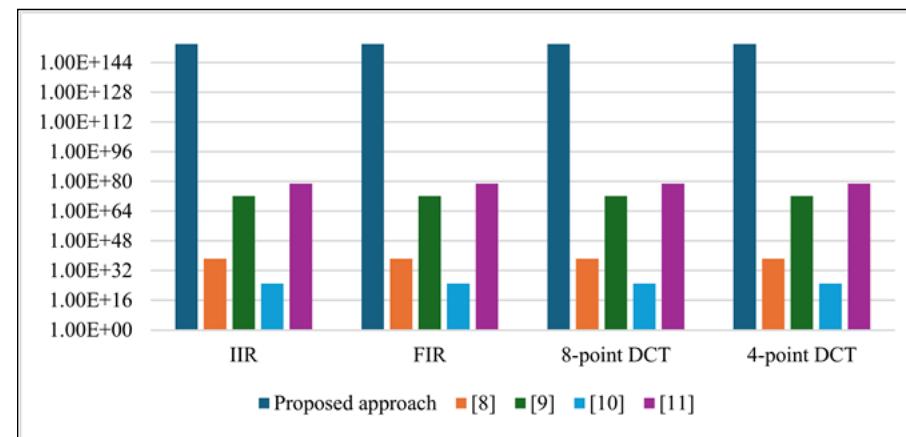

Two standard security metrics *viz.* probability of coincidence (PC) and tamper tolerance (TT)

**Table II**

Comparison of PC corresponding to varying watermark signature size for the proposed approach

The PC is given as:  $PC = (1 - (1/x))^w$

The TT is given as:  $TT = Z^S$

| Watermark size/<br>Benchmarks | IIR      | FIR      | 8-point<br>DCT | 4-point<br>DCT |

|-------------------------------|----------|----------|----------------|----------------|

| 450-bit                       | 7.80E-08 | 2.40E-08 | 6.24E-07       | 1.87E-07       |

| 475-bit                       | 3.14E-08 | 2.40E-08 | 2.82E-07       | 1.87E-07       |

| 500-bit                       | 1.26E-08 | 2.40E-08 | 1.27E-07       | 1.87E-07       |

| 512-bit                       | 8.19E-09 | 2.40E-08 | 8.71E-08       | 1.87E-07       |

**Table III**

Comparison of PC and TT between proposed approach and [8]-[12]

| Benchmarks                             | IIR      |           | FIR      |           | 8-point DCT |           | 4-point DCT |           |

|----------------------------------------|----------|-----------|----------|-----------|-------------|-----------|-------------|-----------|

|                                        | PC       | TT        | PC       | TT        | PC          | TT        | PC          | TT        |

| Proposed approach                      | 8.19E-09 | 1.34E+154 | 2.40E-08 | 1.34E+154 | 8.71E-08    | 1.34E+154 | 1.87E-07    | 1.34E+154 |

| (Sengupta <i>et. al.</i> , 2022) [8]   | 9.51E-03 | 3.40E+38  | 1.40E-03 | 3.40E+38  | 1.71E-02    | 3.40E+38  | 2.58E-04    | 3.40E+38  |

| (Koushanfar <i>et. al.</i> , 2005) [9] | 4.50E-06 | 1.76E+72  | 4.50E-06 | 1.76E+72  | 4.90E-04    | 1.76E+72  | 1.87E-07    | 1.76E+72  |

| (Sengupta <i>et. al.</i> , 2021) [10]  | 4.88E-02 | 9.67E+24  | 1.41E-02 | 9.67E+24  | 7.71E-02    | 9.67E+24  | 4.71E-03    | 9.67E+24  |

| (Sengupta <i>et. al.</i> , 2021) [11]  | 7.27E-05 | 7.41E+78  | 1.45E-06 | 7.41E+78  | 2.44E-04    | 7.41E+78  | 1.87E-07    | 7.41E+78  |

| (Chen <i>et. al.</i> , 2021) [12]      | 1.16E-01 | NA        | 4.84E-02 | NA        | 1.53E-01    | NA        | 2.21E-02    | NA        |

[9] F. Koushanfar, I. Hong, and M. Potkonjak, "Behavioral synthesis techniques for intellectual property protection," *ACM Trans. Design Autom. Electron. Syst.*, vol. 10, no. 3, 523–545, Jul. 2005.

[15] W. Hu, C. Chang, A. Sengupta, S. Bhunia, R. Kastner, H. Li, "An Overview of Hardware Oriented Security and Trust: Threats, Countermeasures and Design Tools", *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, Vol. 40 (6), pp. 1010-1038, 2021.

[16] M. Potkonjak, "Methods and systems for the identification of circuits and circuit designs," *US Patent*, US7017043B1, 2006.

# Results and Analysis

Table IV

Analysis of key strength and probability of decoding the exact key bits ( $P_z$ ) for proposed approach

| Benchmarks  | Key strength | $P_z$    |

|-------------|--------------|----------|

| 4-point DCT | 1.07E+09     | 9.31E-10 |

| FIR         | 2.14E+09     | 4.65E-10 |

| 8-point DCT | 4.29E+09     | 2.32E-10 |

| IIR         | 4.29E+09     | 2.32E-10 |

Table VI

Comparison of implementation runtime of different IP watermarking approaches

| Security approaches                    | Implementation runtime |

|----------------------------------------|------------------------|

| Proposed approach                      | ~350 ms                |

| (Sengupta <i>et. al.</i> , 2022) [8]   | ~193 ms                |

| (Koushanfar <i>et. al.</i> , 2005) [9] | ~453 ms                |

| (Sengupta <i>et. al.</i> , 2021) [10]  | ~270ms                 |

| (Sengupta <i>et. al.</i> , 2021) [11]  | Not available          |

| (Chen <i>et. al.</i> , 2021) [12]      | Not available          |

Table V

Register count, design area, latency, and cost corresponding to selected benchmarks for the proposed approach

| Benchmarks  | Baseline design<br>(no signature) |                         |              |             | Watermarked fault detectable design |                         |              |             | Design cost overhead (%) |

|-------------|-----------------------------------|-------------------------|--------------|-------------|-------------------------------------|-------------------------|--------------|-------------|--------------------------|

|             | Register count                    | Area (um <sup>2</sup> ) | Latency (ps) | Design cost | Register count                      | Area (um <sup>2</sup> ) | Latency (ps) | Design cost |                          |

| IIR         | 28                                | 591.396                 | 2914.67      | 0.805       | 28                                  | 591.396                 | 2914.67      | 0.805       | 0                        |

| FIR         | 20                                | 333.44                  | 2119.76      | 0.864       | 20                                  | 333.44                  | 2119.76      | 0.864       | 0                        |

| 8-point DCT | 32                                | 648.02                  | 4239.52      | 0.921       | 32                                  | 648.02                  | 4239.52      | 0.921       | 0                        |

| 4-point DCT | 16                                | 261.09                  | 2384.73      | 0.875       | 16                                  | 261.09                  | 2384.73      | 0.875       | 0                        |

# Results and Analysis

Fig. 8 and Fig 9 depicts the graphical comparison of PC and TT of proposed approach with [8]-[12]

Fig. 8. Comparison of probability of coincidence (PC) between proposed approach and [8]-[12]

(Note: Lower PC is desirable)

Fig. 9. Comparison of tamper tolerance (TT) between proposed approach and [8]-[11]

(Note: Lower TT is desirable)

# Handling Different Attacks

- 1. Tampering Attack:** The proposed watermarking approach has been evaluated against tampering attack. Tampering attack aims to tamper or remove the embedded watermark.

- 2. Ghost Signature Search Attack (a.k.a Watermark Collision):** The proposed watermarking approach has been evaluated against watermark collision attack/ghost signature search attack.

- 3. Watermark Decoding Attack:** The proposed watermarking approach has been evaluated against watermark decoding attack. In order to exactly decode and prove the embedded watermark constraints in front of third-party authenticator, an attacker needs to completely (and successfully) break all the security layers

# Conclusion

This paper presented a novel hardware watermarking methodology for transient fault-detectable IP designs. The proposed methodology presents a multivariate encoded HLS scheduling based multi-modal security framework for securing fault-detectable IP designs.

# References

- [1] H. Pearce, R. Karri, B. Tan. 2023. High-Level Approaches to Hardware Security: A Tutorial. *ACM Trans. Embed. Compu. Syst.* 22, 3, Article 45, May 2023.

- [2] B. C. Schafer and Z. Wang, "High-Level Synthesis Design Space Exploration: Past, Present, and Future," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 39, no. 10, pp. 2628-2639, Oct. 2020.

- [3] F. Koushanfar, "Hardware metering: A survey," in *Introduction to Hardware Security and Trust*, Tehranipoor, M. and Wang, C. eds. New York, NY, USA: Springer, 2012.

- [4] M. Shayan, K. Basu and R. Karri, "Hardware Trojans Inspired IP Watermarks," *IEEE Design & Test*, vol. 36, no. 6, pp. 72-79, Dec. 2019.

- [5] D. Karaklajić, J. -M. Schmidt and I. Verbauwhede, "Hardware Designer's Guide to Fault Attacks," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 21, no. 12, pp. 2295-2306, Dec. 2013.

- [6] A. Sengupta, M. Rathor "IP Core Steganography for Protecting DSP Kernels used in CE Systems", *IEEE Trans. on Consumer Electronics*, Vol: 65, Issue: 4, pp. 506 – 515, Nov. 2019.

- [7] M. Rostami, F. Koushanfar and R. Karri, "A Primer on Hardware Security: Models, Methods, and Metrics," *Proceedings of the IEEE*, vol. 102, no. 8, pp. 1283-1295, Aug. 2014.

- [8] A. Sengupta and R. Chaurasia, "Securing IP Cores for DSP Applications Using Structural Obfuscation and Chromosomal DNA Impression," *IEEE Access*, vol. 10, pp. 50903-50913, 2022.

- [9] F. Koushanfar, I. Hong, and M. Potkonjak, "Behavioral synthesis techniques for intellectual property protection," *ACM Trans. Design Autom. Electron. Syst.*, vol. 10, no. 3, 523–545, Jul. 2005.

- [10] A. Sengupta and M. Rathor, "Facial Biometric for Securing Hardware Accelerators," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 29, no. 1, pp. 112-123, Jan. 2021.

- [11] A. Sengupta, R. Chaurasia and T. Reddy, "Contact-Less Palmprint Biometric for Securing DSP Coprocessors Used in CE Systems," *IEEE Trans. on Consumer Electronics*, vol. 67, no. 3, pp. 202-213, 2021.

- [12] J. Chen and B. C. Schafer, "Watermarking of Behavioral IPs: A Practical Approach," 2021 IEEE Design, Automation & Test in Europe Conference & Exhibition (DATE), France, pp. 1266-1271, 2021.

- [13] OCL, 15 nm open cell library. [Online], Available: <https://si2.org/open-cell-library/>, last accessed on Feb. 2024.

- [14] Express Benchmark Suite, University of California Santa Barbara (UCSB), Available: <http://www.ece.ucsb.edu/EXPRESS/benchmark/>, Accessed: Feb. 2025.

- [15] W. Hu, C. Chang, A. Sengupta, S. Bhunia, R. Kastner, H. Li, "An Overview of Hardware Oriented Security and Trust: Threats, Countermeasures and Design Tools", *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, Vol. 40 (6), pp. 1010-1038, 2021.

- [16] M. Potkonjak, "Methods and systems for the identification of circuits and circuit designs," US Patent, US7017043B1, 2006.

- [17] A. Sengupta, R. Sedaghat "Swarm Intelligence Driven Design Space Exploration of Optimal k-Cycle Transient Fault Secured Datapath during High Level Synthesis Based on User Power-Delay Budget", Elsevier Journal on Microelectronics Reliability, Volume 55, Issue 6, May 2015, pp. 990-1004, March 2015.

- [18] A. Sengupta and D. Kachave, "Spatial and Temporal Redundancy for Transient Fault-Tolerant Datapath," *IEEE Transactions on Aerospace and Electronic Systems*, vol. 54, no. 3, pp. 1168-1183, June 2018. [19] "Single Event Upsets", Intel, Feb. 2025. Available: <https://www.intel.com/content/www/us/en/support/programmable/support-resources/quality/seu.html>.

- [20] O. Benot, Fault attack, in: H.C.A. van Tilborg, S. Jajodia (Eds.), *Encyclopedia of Cryptography and Security*, Springer, Boston, MA, 2011, [https://doi.org/10.1007/978-1-4419-5906-5\\_505](https://doi.org/10.1007/978-1-4419-5906-5_505).

- [21] S. Rai, A. Rupani, P. Nath and A. Kumar, "Hardware Watermarking Using Polymorphic Inverter Designs Based On Reconfigurable Nanotechnologies," 2019 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2019, pp. 663-669.

- [22] R. Karmakar, S. S. Jana and S. Chattopadhyay, "A Cellular Automata Guided Finite-State-Machine Watermarking Strategy for IP Protection of Sequential Circuits," *IEEE Trans. Emerg. Topics Comput.*, vol. 10, no. 2, pp. 806-823, 1 April-June 2022.

- [23] B. Colombier and L. Bossuet, "Survey of hardware protection of design data for integrated circuits and intellectual properties," *IET Comput. Digit. Techn.*, vol. 8, no. 6, pp. 274–287, 2015.

- [24] A. Cui, C. Chang, S. Tahar and A. T. Abdel-Hamid, "A robust FSM watermarking scheme for IP Protection of sequential circuit design," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 30, no. 5, pp. 678-690, 2011.

- [25] M. Yasin, J. J. Rajendran, O. Sinanoglu, and R. Karri, "On improving the security of logic locking," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 35, no. 9, 1411–1424, 2016.

- [26] F. Koushanfar et al., "Can EDA combat the rise of electronic counterfeiting?," DAC Design Automation Conference 2012, San Francisco, CA, USA, 2012, pp. 133-138.

- [27] S. M. Plaza and I. L. Markov, "Solving the Third-Shift Problem in IC Piracy With Test-Aware Logic Locking," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 34, no. 6, pp. 961-971, June 2015.

- [28] A. Sengupta, S. Mohanty, "Advanced Encryption Standard (AES) and its Hardware Watermarking for Ownership Protection", IET, IP Core Protection and Hardware-Assisted Security for Consumer Electronics, 2019, Book ISBN: 978-1-78561-799-7, e-ISBN: 978-1-78561-800-0.

- [29] C. Paar, J. Pelzl "Understanding Cryptography - A Textbook for Students and Practitioners", Springer-Verlag, eBook ISBN 978-3-642-04101-3, Number of Pages: XVIII, 372, Nov 2009.

# THANK YOU