# **LOW COST FAULT RELIABILITY AND TROJAN SECURITY AWARE HIGH LEVEL SYNTHESIS FOR APPLICATION SPECIFIC DATAPATH PROCESSORS**

**Ph.D. Thesis**

**By**

**SAUMYA BHADAURIA**

**DISCIPLINE OF COMPUTER SCIENCE & ENGINEERING

INDIAN INSTITUTE OF TECHNOLOGY INDORE

JANUARY 2016**

# LOW COST FAULT RELIABILITY AND TROJAN SECURITY AWARE HIGH LEVEL SYNTHESIS FOR APPLICATION SPECIFIC DATAPATH PROCESSORS

A THESIS

*Submitted in partial fulfillment of the

requirements for the award of the degree

of

DOCTOR OF PHILOSOPHY*

*by*

**SAUMYA BHADAURIA**

**DISCIPLINE OF COMPUTER SCIENCE & ENGINEERING

INDIAN INSTITUTE OF TECHNOLOGY INDORE**

**JANUARY 2016**

## CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the thesis entitled **LOW COST FAULT RELIABILITY AND TROJAN SECURITY AWARE HIGH LEVEL SYNTHESIS FOR APPLICATION SPECIFIC DATAPATH PROCESSORS** in the partial fulfillment of the requirements for the award of the degree of **DOCTOR OF PHILOSOPHY** and submitted in the **DISCIPLINE OF COMPUTER SCIENCE & ENGINEERING, INDIAN INSTITUTE OF TECHNOLOGY INDORE**, is an authentic record of my own work carried out during the time period from July 2013 to January 2016 under the supervision of Dr. Anirban Sengupta, Assistant Professor, Indian Institute of Technology Indore.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other institute.

**Signature of the student with date**

**SAUMYA BHADAURIA**

---

This is to certify that the above statement made by the candidate is correct to the best of my/our knowledge.

Signature of Thesis Supervisor with date

**(Dr. Anirban Sengupta)**

---

**SAUMYA BHADAURIA** has successfully given his/her Ph.D. Oral Examination held on

Signature(s) of Thesis Supervisor(s)

Date:

Convener, DPGC

Date:

Signature of PSPC Member #1

Date:

Signature of PSPC Member #1

Date:

Signature of External Examiner

Date:

## ACKNOWLEDGEMENTS

First of all, I would like to thank my parents and my brother, Ishan, for their strong belief in me and for always being a constant source of motivation and guidance. This thesis would not have been possible without them.

I would like to express my gratitude to my supervisor Dr. Anirban Sengupta for providing me the opportunity to do work under his supervision, without his guidance and directions to solve the challenging tasks this research work could not be completed. I have learned a lot from him.

Besides my advisor, I also owe a mention to Dr. Abhishek Srivastava, Dr. Surya Prakash and Dr. Shanmugam Dhinakaran for their valuable feedbacks on my research work throughout these years. I am grateful to Dr. Kapil Ahuja, Head, CSE Discipline for all the help and cooperation.

Special thanks to Navneet, Rajendra and Vipul for their moral support and valuable opinions at times. It has been a great pleasure to work with many talented colleagues during my years of work at IIT Indore. I would like to thank all my past and present colleagues and all my friends for their help and support.

At last, I would like to thank IIT Indore, DST, CSIR to help me financially and providing me an opportunity to showcase my research at international grounds.

**DEDICATED TO MY FAMILY**

## ABSTRACT

With changing trends in technology and to effectively compete in the market, designers are focussing on attempts to optimize Very Large Scale Integration (VLSI) digital systems. Attempts to devise design systems with higher performance, accuracy and efficiency along with lower overall cost are being made. In order to achieve this, High Level Synthesis (HLS) / architectural synthesis has come into force. However, there is a paradigm shift in the area of HLS as more and more designs are suffering from reliability and hardware security issues. These are expected to become the key focus due to massive scaling in nanometre technology and globalization involved in the VLSI design process. This thesis proposes methodologies for generating low cost security solutions for both transient fault and hardware Trojan with respect to data intensive and control intensive applications during design of application specific datapath processor at behavioural level. This thesis solves five different types of problems in generating reliable/hardware secured designs: **a)** Problem of design Space Exploration (DSE) during power-performance trade-off for data intensive applications that produces high quality design solutions. In addition, a novel Bacterial Foraging Optimization (BFO) driven DSE methodology is proposed which explores the design points in the design space. A novel chemotaxis, replication and elimination-dispersal algorithm is proposed which generates the design points. **b)** Problem of exploration of low cost optimal  $k$ -cycle transient fault secured datapath during power-performance trade-off for data intensive applications. A novel fault security algorithm for handling single and multi-cycle transient faults is proposed. A novel multi-cycle Single Event Transient (SET) fault security aware multi objective DSE methodology that explores an optimal combination of transient fault secured (Double Modular Redundant) DMR datapath configuration has been proposed. Moreover, a novel scheme for selecting appropriate edges for inserting cuts in the scheduled Data Flow Graphs (DFG) minimizing delay overhead associated with transient fault security, a novel execution time model for estimating the execution time of a transient fault secured/Trojan secured design during DSE process, a novel fitness function, used for design quality assessment in DSE process has been proposed. **c)** Problem of exploration of low cost optimal  $k$ -cycle transient fault secured datapath during area-delay trade-off for control intensive applications. a novel multi-cycle SET fault security aware multi objective DSE methodology that explores

an optimal combination of transient fault secured DMR datapath configuration and loop Unrolling Factor (UF) for Control Data Flow Graphs (CDFG) has been proposed. Moreover, a novel estimation model for computation of execution delay of a loop unrolled CDFG (based on a resource configuration explored) without tediously unrolling the entire CDFG for the specified loop value has been proposed. **d)** Problem of exploration of low cost optimal  $k$ -cycle transient fault tolerant datapath based on power-performance tradeoff for data intensive applications. In relation to this, a novel multi-cycle transient fault tolerant algorithm that has capability to isolate original and duplicate units in a DMR with respect to the transient fault has been proposed. Moreover, a novel equivalent circuit that works with DMR systems performs the function of extracting the correct output from the DMR design has been proposed. **e)** Problem of exploration of low cost optimal Trojan secured datapath during behavioural synthesis for data intensive applications has been tackled. A novel encoding scheme for representing bacterium in the design space (comprising of candidate datapath resource configuration and vendor allocation information for hardware Trojan secured datapath) has been proposed. Moreover, a novel exploration process of an efficient vendor allocation procedure that assists in yielding a low cost hardware Trojan secured datapath within user constraints has been proposed.

# LIST OF PUBLICATIONS

## International Journals (5)

1. Saumya Bhaduria, Anirban Sengupta “Adaptive bacterial foraging optimization driven Design Space Exploration: Exploring area-performance tradeoff during HLS”, *Elsevier Journal on Applied Mathematics and Computations*, Volume 269, pp. 265–278, Oct 2015. (**5 yr Impact Factor ~1.686**)

2. Anirban Sengupta, Saumya Bhaduria, “Automated Design Space Exploration of Multi-Cycle Transient Fault Detectable Datapath based on Multi-Objective User Constraints for Application Specific Computing”, *Elsevier Journal on Advances in Engineering Software*, Volume 82, pp. 14- 24, April 2015. (**5 yr Impact Factor ~1.5**)

3. Anirban Sengupta, Saumya Bhaduria, “Bacterial Foraging Driven Exploration of Multi Cycle Fault Tolerant Datapath based on Power-Performance Tradeoff in High Level Synthesis”, *Elsevier Journal on Expert Systems With Applications*, Volume 42, pp. 4719 - 4732, Jan 2015. (**5yr Impact Factor = 2.339**).

4. Saumya Bhaduria, Anirban Sengupta, “Multi-Cycle Single Event Transient Fault Security Aware MO-DSE for Single loop CDFGs in HLS”, *IEEE VLSI Circuits & Systems Letters*, Volume 1, Issue 2, Oct 2015.

5. Anirban Sengupta, Saumya Bhaduria, “Exploration of Multi-Objective Tradeoff During High Level Synthesis Using Bacterial Chemotaxis and Dispersal”, *Elsevier Journal on Procedia Computer Science*, Volume 35, Issue C, pp. 63 -72, Sep 2014.

## Peer Reviewed Conferences (7)

6. Anirban Sengupta, Saumya Bhaduria, “Untrusted Third Party Digital IP cores: Power-Delay Trade-off Driven Exploration of Hardware Trojan Secured Datapath during High Level Synthesis”, Proceedings of *25th IEEE/ACM Great Lake Symposium on VLSI (GLSVLSI)*, Pennsylvania, pp. 167-172, May 2015. (**DOUBLE BLIND REVIEW**).

7. Anirban Sengupta, Saumya Bhaduria, “Automated Design Space Exploration of Transient Fault Detectable Datapath Based on User Specified Power and Delay Constraints”, Proceedings of *33rd VLSI - Design Automation & Test (VLSI - DAT), Taiwan*, pp. 1-4, April 2015. (DOUBLE BLIND REVIEW) Note- *Amongst top 10 EDA/VLSI conferences*

8. Anirban Sengupta, Saumya Bhaduria, “User Power-Delay Budget Driven PSO Based Design Space Exploration of Optimal  $k$ -cycle Transient Fault Secured Datapath during High Level Synthesis”, Proceedings of *16th IEEE International Symposium on Quality Electronic Design (ISQED 2015)*, California, USA, pp. 289 - 292, March 2015. (DOUBLE BLIND REVIEW) Note- *Amongst top 10 EDA/VLSI conferences*

9. Saumya Bhaduria, Anirban Sengupta, “A High Level Synthesis Approach for Exploring Low Cost  $k$ -cycle Transient Fault Secured Solution”, *21st Asia South Pacific-Design Automation Conference (ASP-DAC)*, Jan 2016, Accepted.

10. Anirban Sengupta, Saumya Bhaduria, “Automated Exploration of Datapath in High Level Synthesis using Temperature Dependent Bacterial Foraging Optimization Algorithm”, Proceedings of *27th IEEE Canadian Conference on Electrical and Computer Engineering, Toronto*, pp. 68 -73, May 2014.

11. Anirban Sengupta, Saumya Bhaduria, “Error Masking of Transient Faults: Exploration of a Fault Tolerant Datapath Based on User Specified Power and Delay Budget”, Proceedings of *13th IEEE International Conference on Information Technology*, pp. 345 – 350, Dec 2014. (DOUBLE BLIND REVIEW)

12. Saumya Bhaduria, Anirban Sengupta, “Secure Information Processing during System level: Exploration of an Optimized Trojan Secured Datapath for CDFGs during HLS based on User Constraints”, Proceedings of *1<sup>st</sup> IEEE iNIS 2015* Special Session, Accepted, 2015.

# TABLE OF CONTENTS

|                                                                                                                   |              |

|-------------------------------------------------------------------------------------------------------------------|--------------|

| <b>ABSTRACT</b>                                                                                                   | <b>VI</b>    |

| <b>LIST OF PUBLICATIONS</b>                                                                                       | <b>VIII</b>  |

| <b>LIST OF FIGURES</b>                                                                                            | <b>XIV</b>   |

| <b>LIST OF TABLES</b>                                                                                             | <b>XVI</b>   |

| <b>NOMENCLATURE</b>                                                                                               | <b>XVIII</b> |

| <b>ACRONYMS</b>                                                                                                   | <b>XXI</b>   |

| <br>                                                                                                              |              |

| <b>1. Chapter 1</b>                                                                                               |              |

| <b>    Introduction</b>                                                                                           | <b>1</b>     |

| 1.1 Preamble                                                                                                      | 1            |

| 1.2 Circuit Design and Synthesis                                                                                  | 1            |

| 1.3 High Level Synthesis (HLS) Details                                                                            | 2            |

| 1.4 Theoretical Background on HLS                                                                                 | 3            |

| 1.5 Phases of HLS                                                                                                 | 4            |

| 1.6 Why HLS?                                                                                                      | 6            |

| 1.7 Thesis Organization                                                                                           | 7            |

| <br>                                                                                                              |              |

| <b>2. Chapter 2</b>                                                                                               |              |

| <b>    Previous Work and Thesis Contribution</b>                                                                  | <b>8</b>     |

| 2.1 Related Work                                                                                                  | 8            |

| 2.2 Objective                                                                                                     | 13           |

| 2.3 Summary of Contribution                                                                                       | 13           |

| <br>                                                                                                              |              |

| <b>3. Chapter 3</b>                                                                                               |              |

| <b>    Adaptive Bacterial Foraging Driven Datapath Optimization: Exploring Power-performance Trade-off in HLS</b> | <b>16</b>    |

| 3.1 Description of Proposed Methodology                                                                           | 16           |

| 3.1.1 Problem Formulation                                                                                         | 16           |

| 3.1.2 Motivation of using BFOA in Context of Proposed Problem                                                     | 17           |

| 3.1.3 Proposed BFOA Driven DSE Methodology                                                                        | 17           |

| 3.1.4 Models for Evaluation of Design Points During BFOA                                                          | 19           |

|           |                                                                                                                                                                           |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2       | Description of Proposed Methodology with Demonstration                                                                                                                    | 21 |

| 3.2.1     | Module Library Information and Operating Constraints                                                                                                                      | 21 |

| 3.2.2     | Maximum Threshold                                                                                                                                                         | 22 |

| 3.2.3     | Boundary Constraints Check Module                                                                                                                                         | 22 |

| 3.2.4     | Initialization of Bacterium                                                                                                                                               | 22 |

| 3.2.5     | Calculation of Fitness of a Bacterium                                                                                                                                     | 23 |

| 3.2.6     | Determination of New Configuration of the Particle                                                                                                                        | 25 |

| 3.2.7     | Termination Criteria                                                                                                                                                      | 30 |

| 3.3       | Summary                                                                                                                                                                   | 30 |

| <b>4.</b> | <b>Chapter 4</b>                                                                                                                                                          |    |

|           | <b>Automated Design Space Exploration of Multi-Cycle Transient Fault Detectable Datapath based on Multi-Objective User Constraints for Application Specific Computing</b> | 31 |

| 4.1       | Problem Formulation                                                                                                                                                       | 32 |

| 4.2       | Proposed Methodology                                                                                                                                                      | 32 |

| 4.2.1     | Motivation                                                                                                                                                                | 32 |

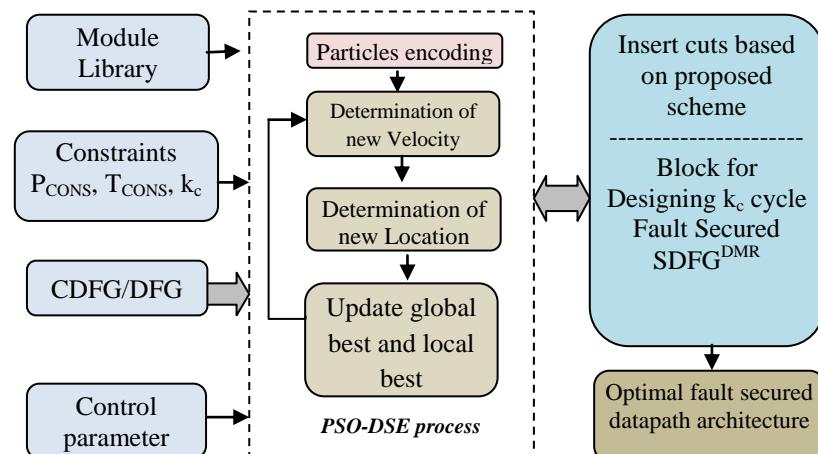

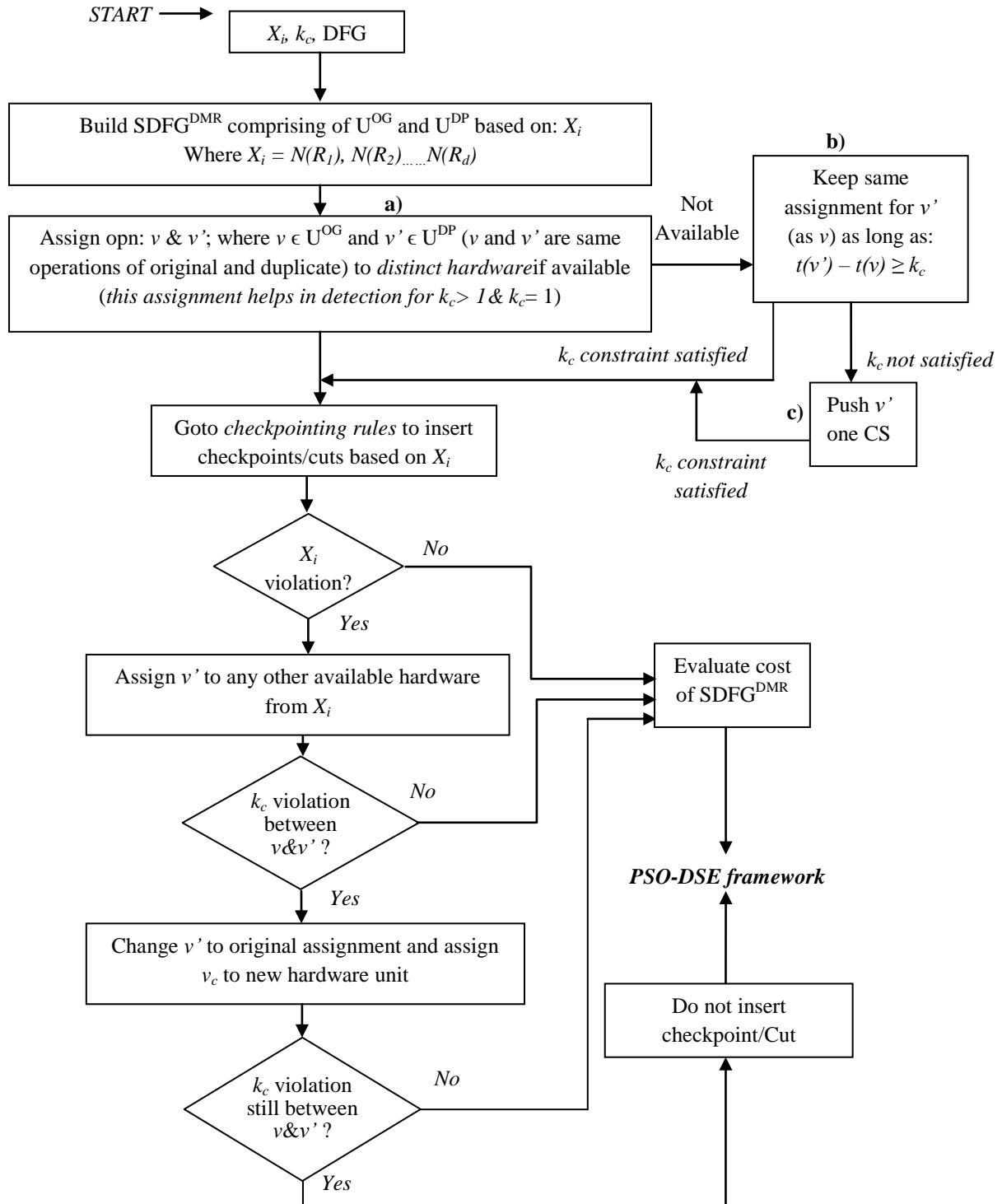

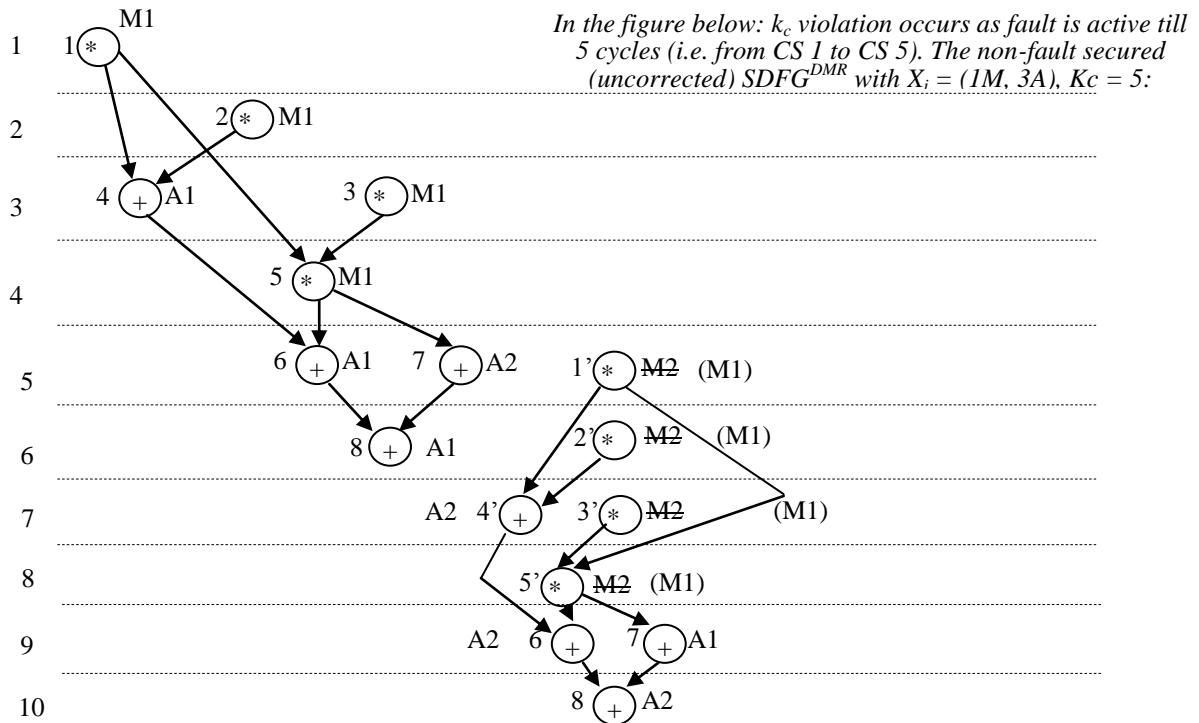

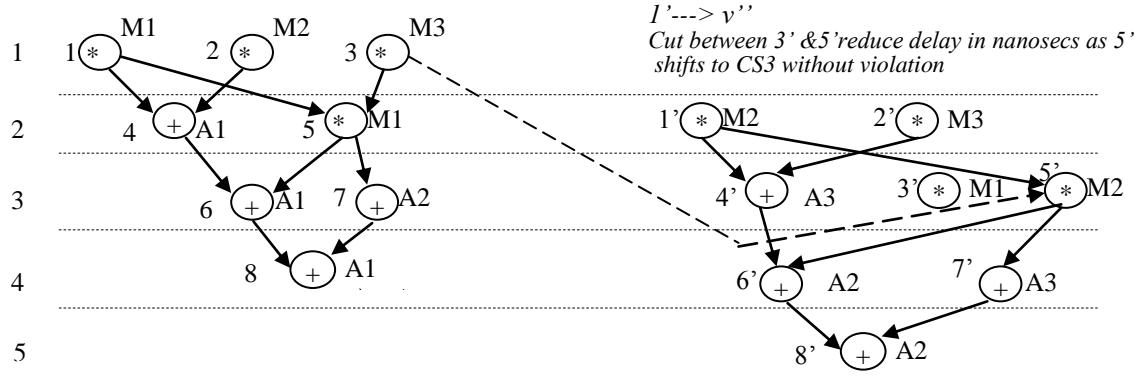

| 4.2.2     | Proposed Framework                                                                                                                                                        | 34 |

| 4.3       | Proposed Evaluation Models                                                                                                                                                | 43 |

| 4.4       | Demonstration of PSO-DSE Methodology                                                                                                                                      | 45 |

| 4.5       | Stopping Criteria (Z)                                                                                                                                                     | 47 |

| 4.6       | Summary                                                                                                                                                                   | 48 |

| <b>5.</b> | <b>Chapter 5</b>                                                                                                                                                          |    |

|           | <b>Multi-Cycle Single Event Transient Fault Security Aware MO-DSE for Single loop CDFGs in HLS</b>                                                                        | 49 |

| 5.1       | Problem Formulation                                                                                                                                                       | 49 |

| 5.2       | The Proposed Framework and Mapping Process                                                                                                                                | 50 |

| 5.3       | Proposed Evaluation Models and Formulation                                                                                                                                | 50 |

| 5.4       | Proposed Methodology                                                                                                                                                      | 53 |

| 5.5       | Stopping Condition                                                                                                                                                        | 58 |

| 5.6       | Summary                                                                                                                                                                   | 58 |

| <b>6.</b> | <b>Chapter 6</b>                                                                                                                                                          |    |

|           | <b>Bacterial Foraging Driven Exploration of Multi Cycle Fault Tolerant Datapath based on Power-Performance Tradeoff in High Level</b>                                     | 59 |

|                                                                                                                                                         |                                                                                                                                                                                          |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Synthesis</b>                                                                                                                                        |                                                                                                                                                                                          |     |

| 6.1                                                                                                                                                     | Problem Formulation                                                                                                                                                                      | 59  |

| 6.2                                                                                                                                                     | Proposed Framework                                                                                                                                                                       | 60  |

| 6.3                                                                                                                                                     | Proposed Evaluation Models                                                                                                                                                               | 69  |

| 6.4                                                                                                                                                     | Termination Criteria                                                                                                                                                                     | 71  |

| 6.5                                                                                                                                                     | Summary                                                                                                                                                                                  | 71  |

| <b>7. Chapter 7</b>                                                                                                                                     |                                                                                                                                                                                          |     |

| <b>Untrusted Third Party Digital IP cores: Power-Delay Trade-off Driven Exploration of Hardware Trojan Secured Datapath during High Level Synthesis</b> |                                                                                                                                                                                          | 72  |

| 7.1                                                                                                                                                     | Problem Formulation                                                                                                                                                                      | 73  |

| 7.2                                                                                                                                                     | Proposed Methodology                                                                                                                                                                     | 74  |

| 7.3                                                                                                                                                     | Termination criteria                                                                                                                                                                     | 79  |

| 7.4                                                                                                                                                     | Summary                                                                                                                                                                                  | 80  |

| <b>8. Chapter 8</b>                                                                                                                                     |                                                                                                                                                                                          |     |

| <b>Results and Analysis</b>                                                                                                                             |                                                                                                                                                                                          | 81  |

| 8.1                                                                                                                                                     | Experimental Results: Adaptive Bacterial foraging driven Datapath Optimization: Exploring Power-performance Trade-off in High level synthesis                                            | 81  |

| 8.2                                                                                                                                                     | Experimental Results: Automated Design Space Exploration of Multi-Cycle Transient Fault Detectable Datapath based on Multi-Objective User Constraints for Application Specific Computing | 91  |

| 8.3                                                                                                                                                     | Experimental Results: Multi-Cycle Single Event Transient Fault Security Aware MO-DSE for Single loop CDFGs in HLS                                                                        | 93  |

| 8.4                                                                                                                                                     | Experimental Results: Bacterial Foraging Driven Exploration of Multi Cycle Fault Tolerant Datapath based on Power-Performance Tradeoff in High Level Synthesis                           | 97  |

| 8.5                                                                                                                                                     | Experimental Results: Untrusted Third Party Digital IP cores: Power-Delay Trade-off Driven Exploration of Hardware Trojan Secured Datapath during High Level Synthesis                   | 104 |

|                                   |             |     |

|-----------------------------------|-------------|-----|

| <b>9. Chapter 9</b>               |             |     |

| <b>Conclusion and Future work</b> |             |     |

| 9.1                               | Conclusion  | 110 |

| 9.2                               | Future work | 111 |

| <b>References</b>                 |             |     |

|                                   |             | 112 |

## LIST OF FIGURES

|               |                                                                                      |    |

|---------------|--------------------------------------------------------------------------------------|----|

| Figure 1.1    | Sample Behavioural description                                                       | 3  |

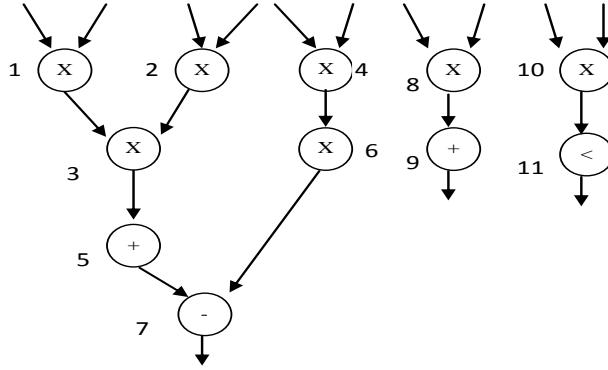

| Figure 1.2    | Sample Data Flow Graph                                                               | 3  |

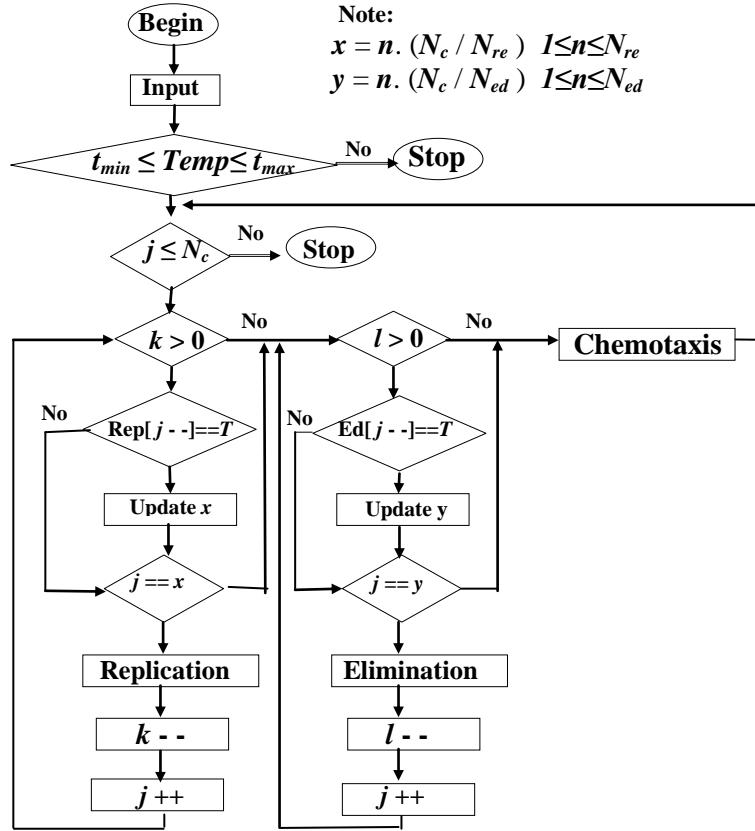

| Figure 3.1    | Proposed BFOA –DSE Methodology                                                       | 18 |

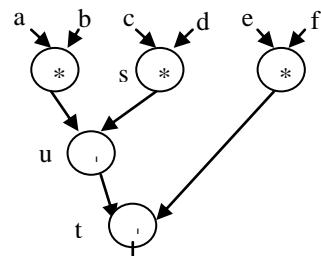

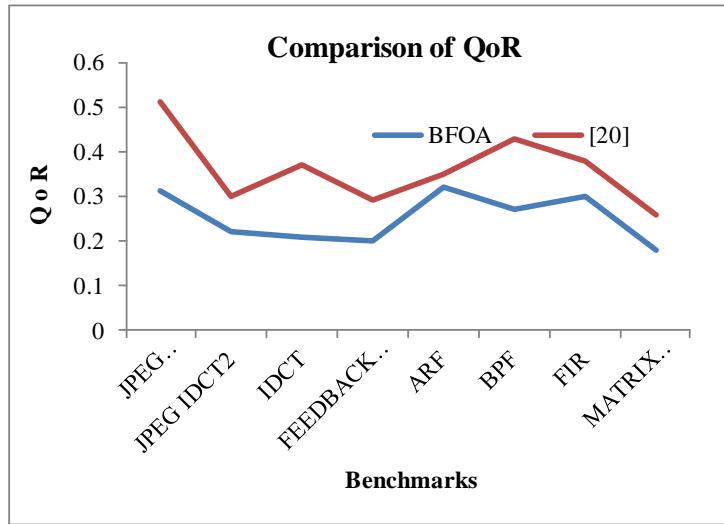

| Figure 3.2    | DFG of HAL Benchmark                                                                 | 21 |

| Figure 3.3    | Pseudo code for Proposed Chemotaxis Algorithm                                        | 24 |

| Figure 3.4    | Pseudo code for Proposed Replication Algorithm                                       | 27 |

| Figure 3.5    | Pseudo code for Proposed Elimination-Dispersal Algorithm                             | 28 |

| Figure 4.1    | Scheduled Sequencing Graph with Data Registers                                       | 32 |

| Figure 4.2    | Block Diagram of Proposed Approach                                                   | 33 |

| Figure 4.3    | Pseudo code for PSO-DSE                                                              | 35 |

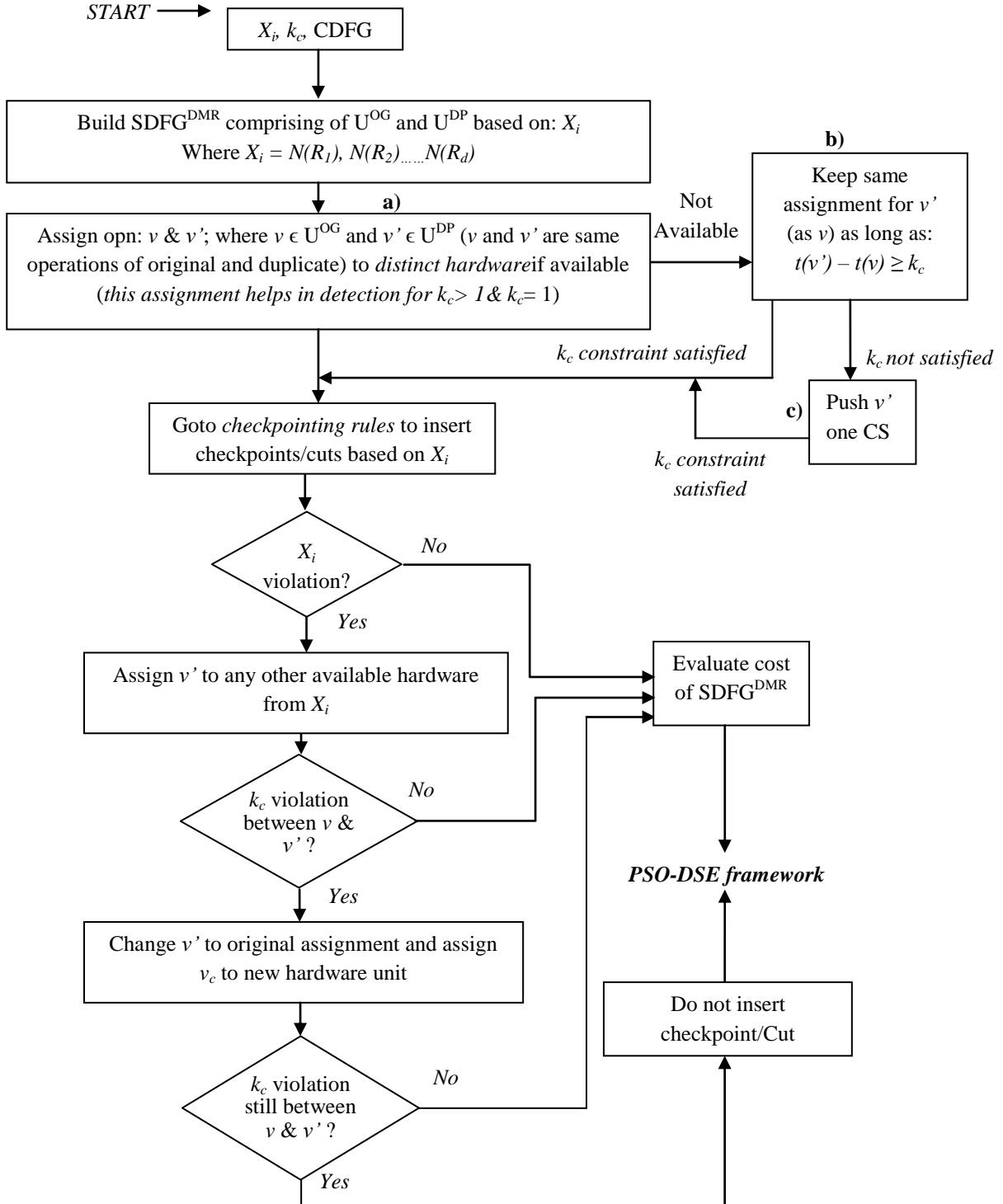

| Figure 4.4    | Algorithm for generating a $k_c$ Fault Secured SDFG <sup>DMR</sup>                   | 36 |

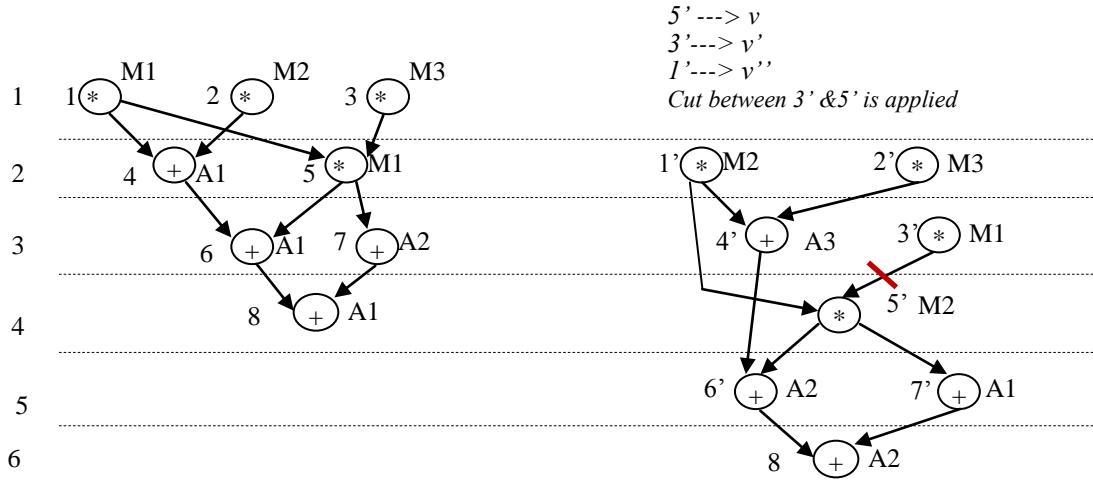

| Figure 4.5    | Uncorrected 5-cycle fault secured SDFG <sup>DMR</sup>                                | 38 |

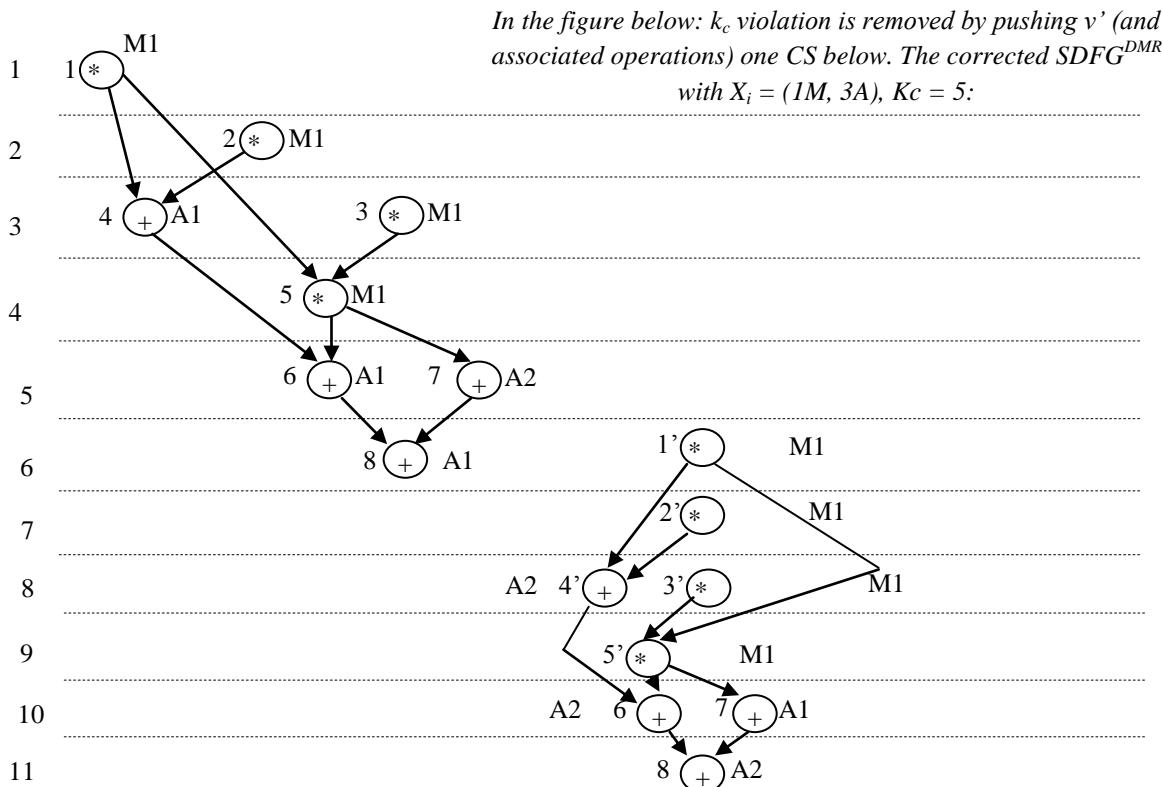

| Figure 4.6    | Corrected 5-cycle Fault Secured SDFG <sup>DMR</sup>                                  | 39 |

| Figure 4.7    | Example for C1                                                                       | 40 |

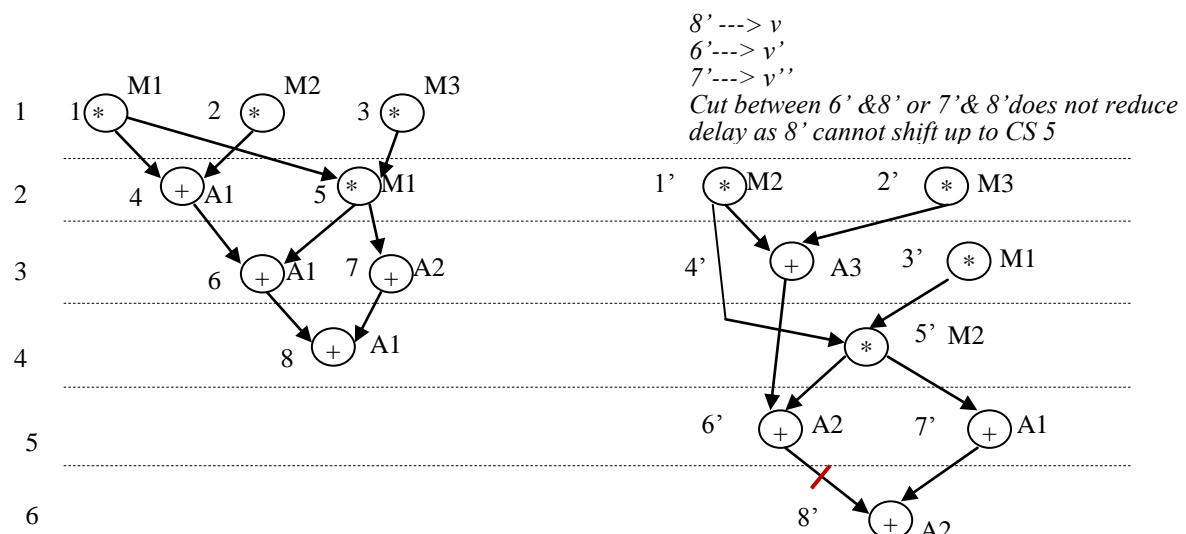

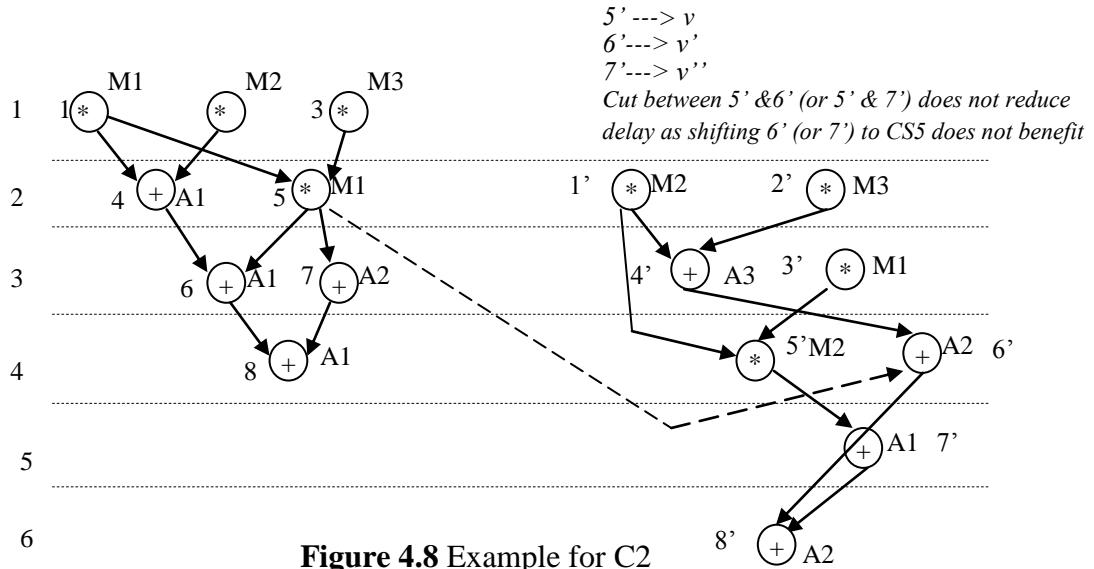

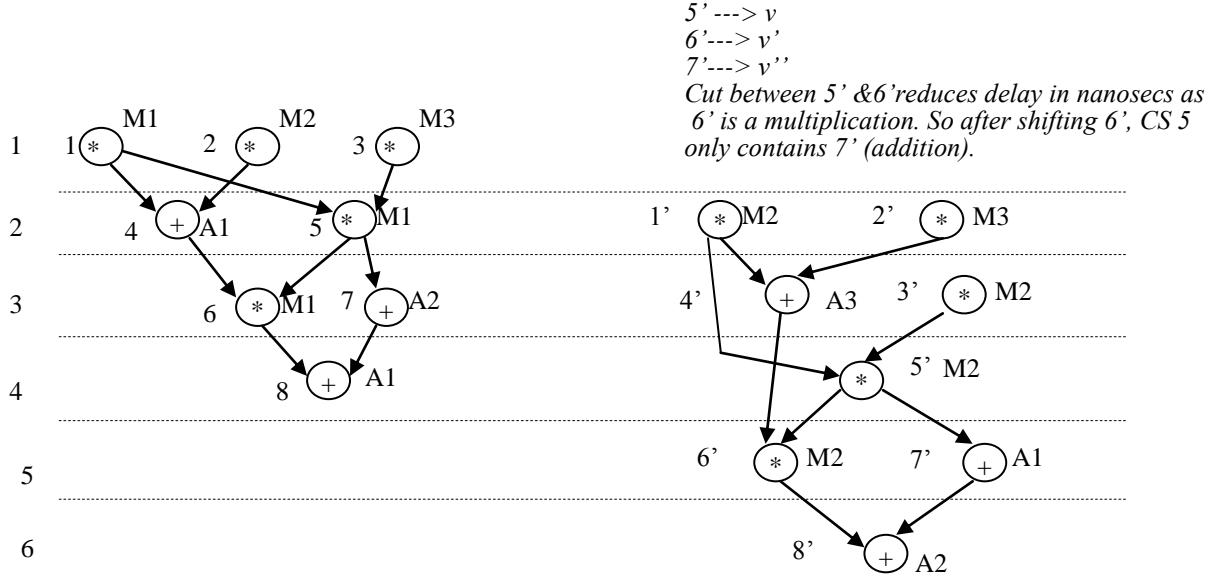

| Figure 4.8    | Example for C2                                                                       | 41 |

| Figure 4.9    | Example for C3 Before Cut                                                            | 42 |

| Figure 4.10   | Example for C4 Before Cut                                                            | 43 |

| Figure 4.11   | Example for Condition 4 After Cut                                                    | 43 |

| Figure 4.12   | Adaptive End Terminal Perturbation Algorithm                                         | 45 |

| Figure 4.13   | Adaptive Rotation Mutation Algorithm                                                 | 46 |

| Figure 5.1    | Proposed Multi-cycle Transient Fault Security Aware DSE During Behavioural Synthesis | 50 |

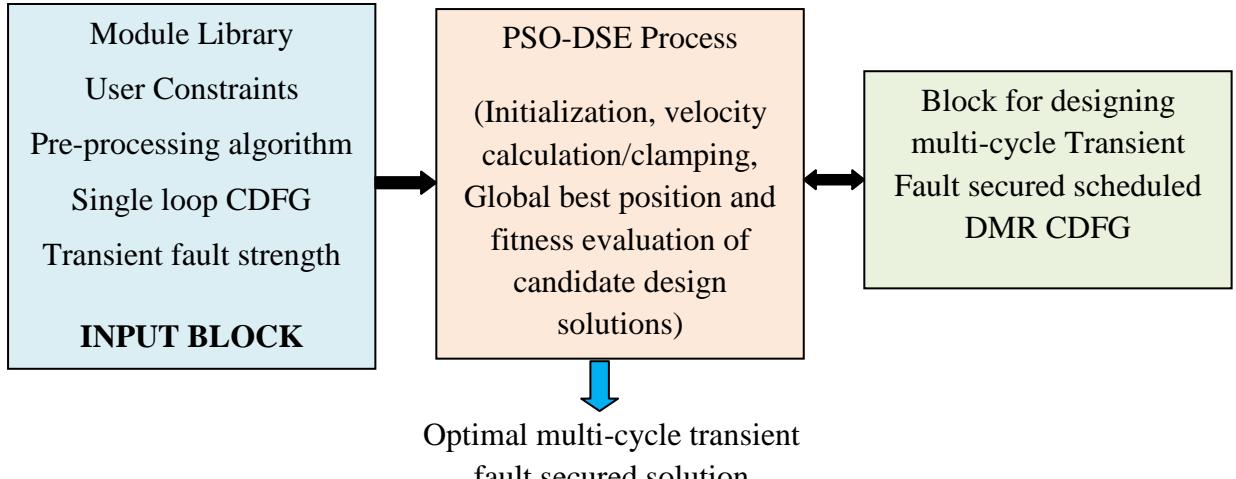

| Figure 5.2(a) | FFT Loop                                                                             | 51 |

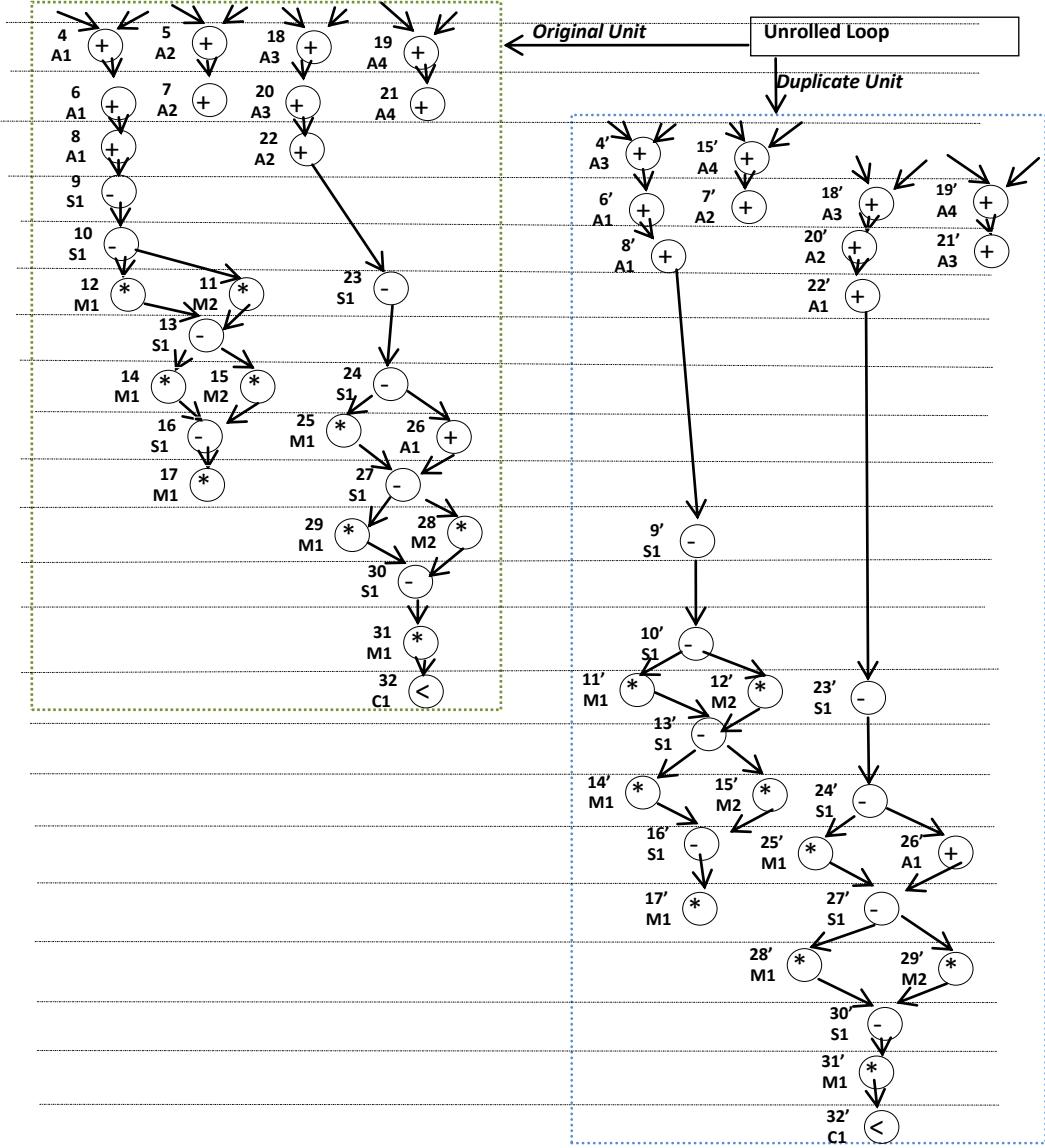

| Figure 5.2(b) | FFT Loop Unrolled Twice                                                              | 51 |

| Figure 5.3    | $k_c$ Fault Secured SCDFG <sup>DMR</sup> of FFT Loop body for Resource               | 52 |

|              |                                                                                                                                                                |     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | configuration (4(+), 2(*), 1(-), 1(<), UF=2) at I=4 and $k_c=2$                                                                                                |     |

| Figure 5.4   | Pre-processing of UF                                                                                                                                           | 54  |

| Figure 5.5   | Algorithm for Inclusion of Some Special UFs                                                                                                                    | 54  |

| Figure 5.6   | Algorithm for Generating a $k_c$ Fault Secured SCDFG <sup>DMR</sup>                                                                                            | 56  |

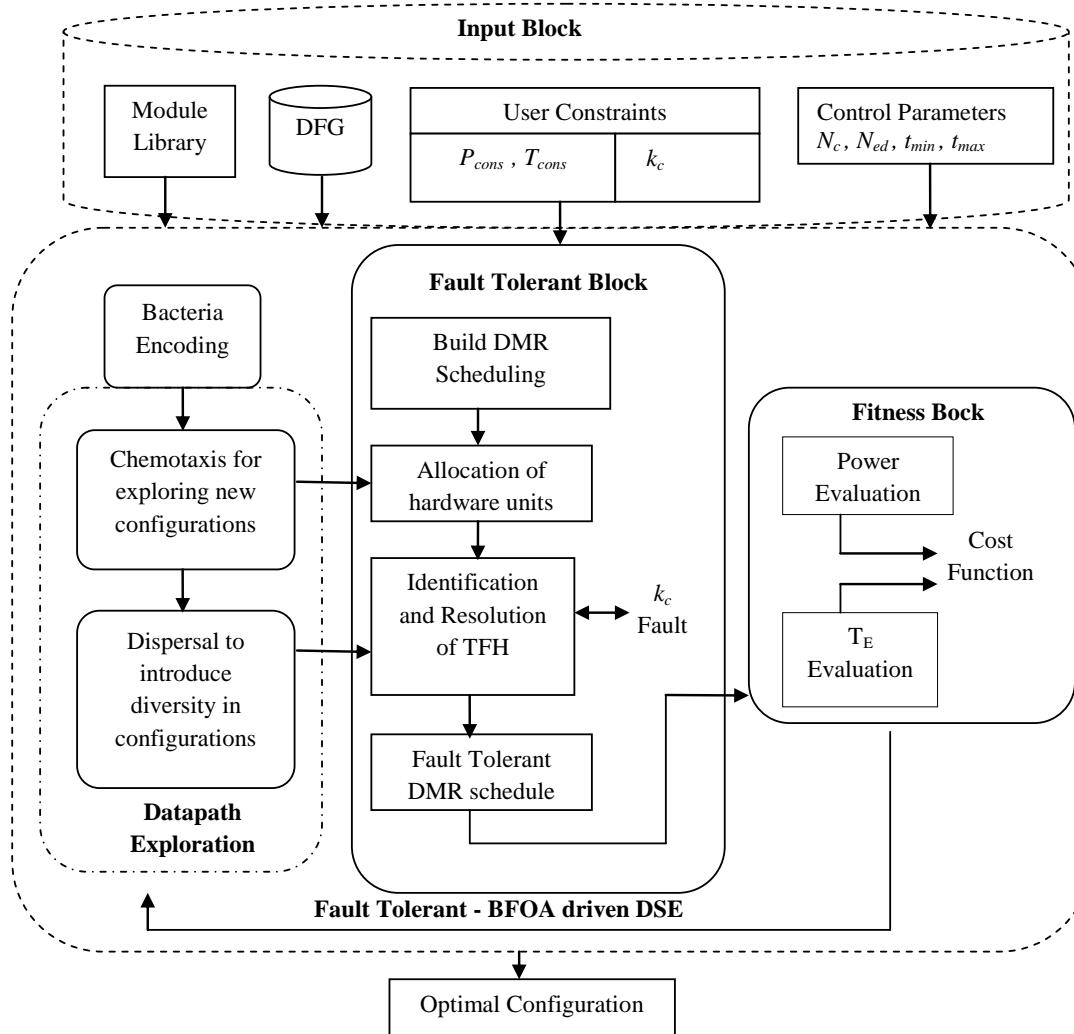

| Figure 6.1   | Proposed Multi Objective Multi Cycle Fault Tolerant BFOA-DSE Approach                                                                                          | 60  |

| Figure 6.2   | Pseudo code for Multi Cycle Fault Tolerant Algorithm                                                                                                           | 62  |

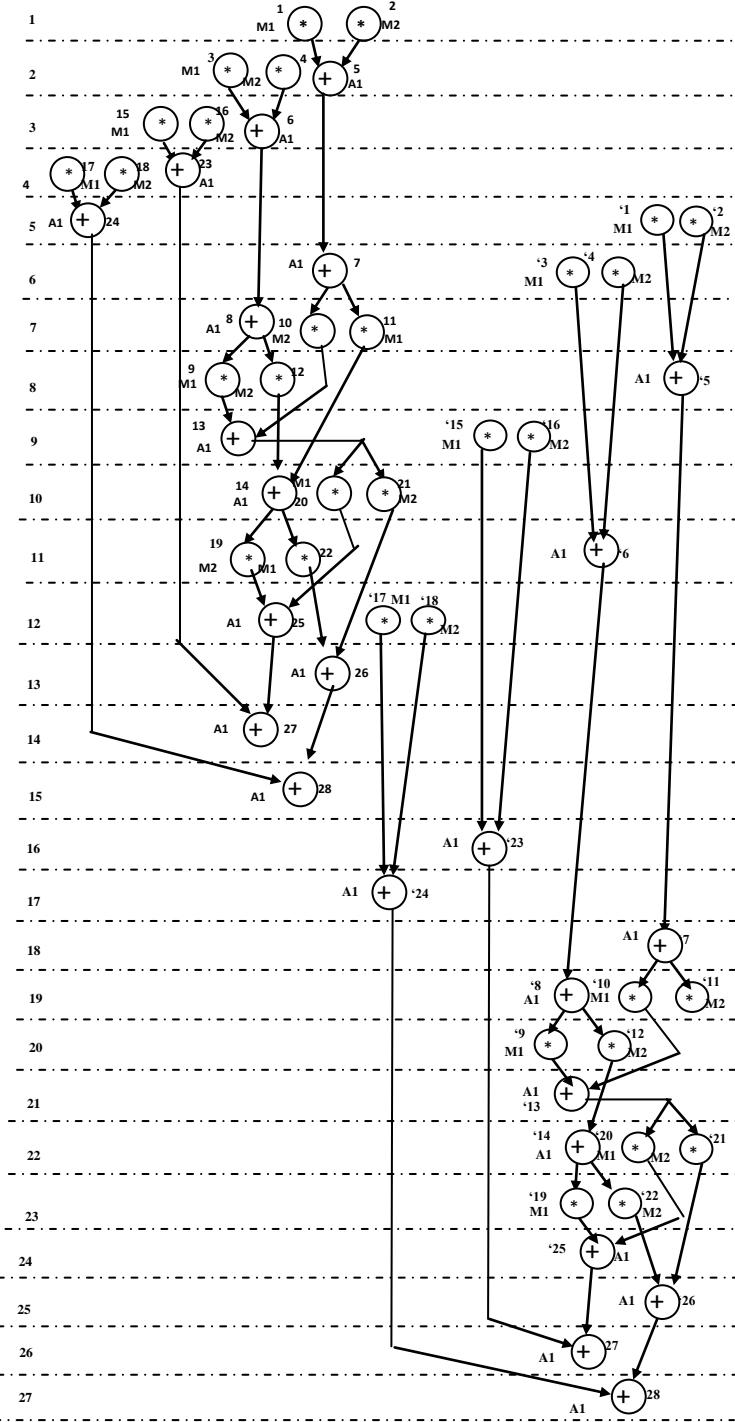

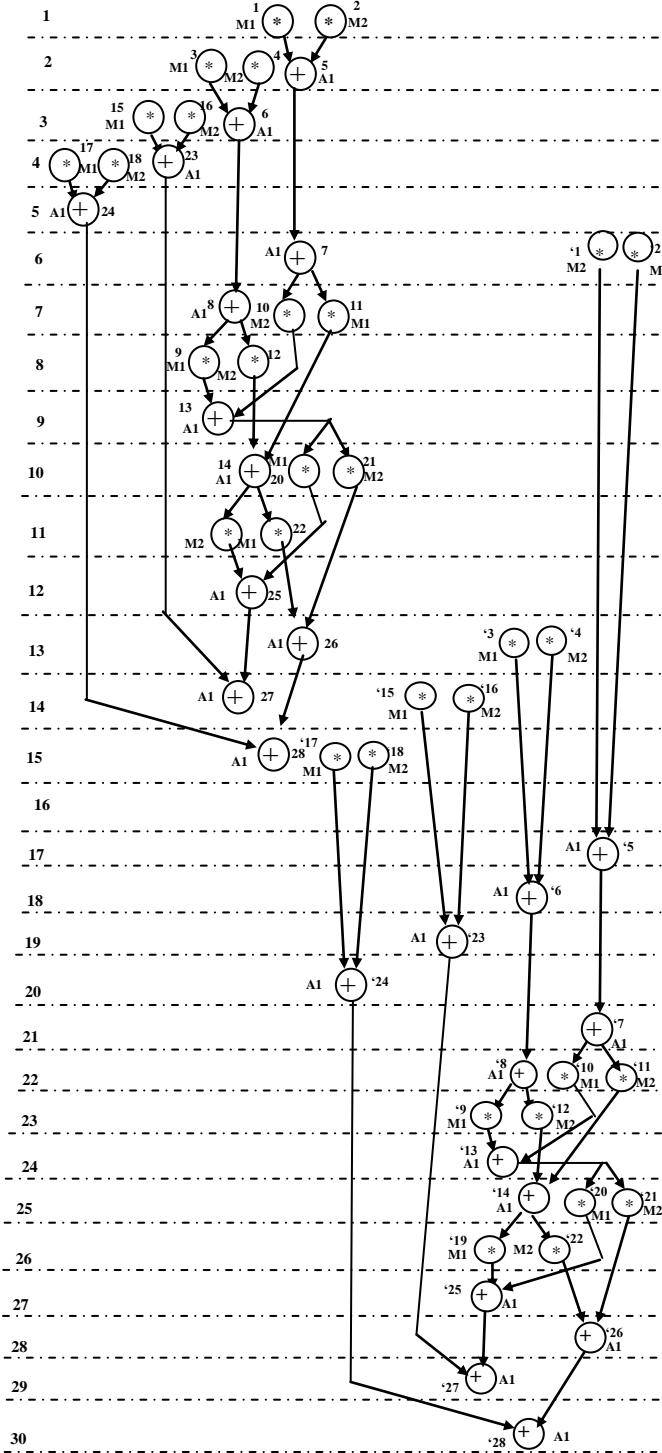

| Figure 6.3 : | SDFG <sup>DMR</sup> of ARF with $X_i = 1(+), 2(*)$                                                                                                             | 63  |

| Figure 6.4:  | Intermediate Fault Tolerant SDFG <sup>DMR</sup> of ARF for $k_c = 2$                                                                                           | 64  |

| Figure 6.5   | Fault Tolerant SDFG <sup>DMR</sup> of ARF for $k_c = 2$                                                                                                        | 65  |

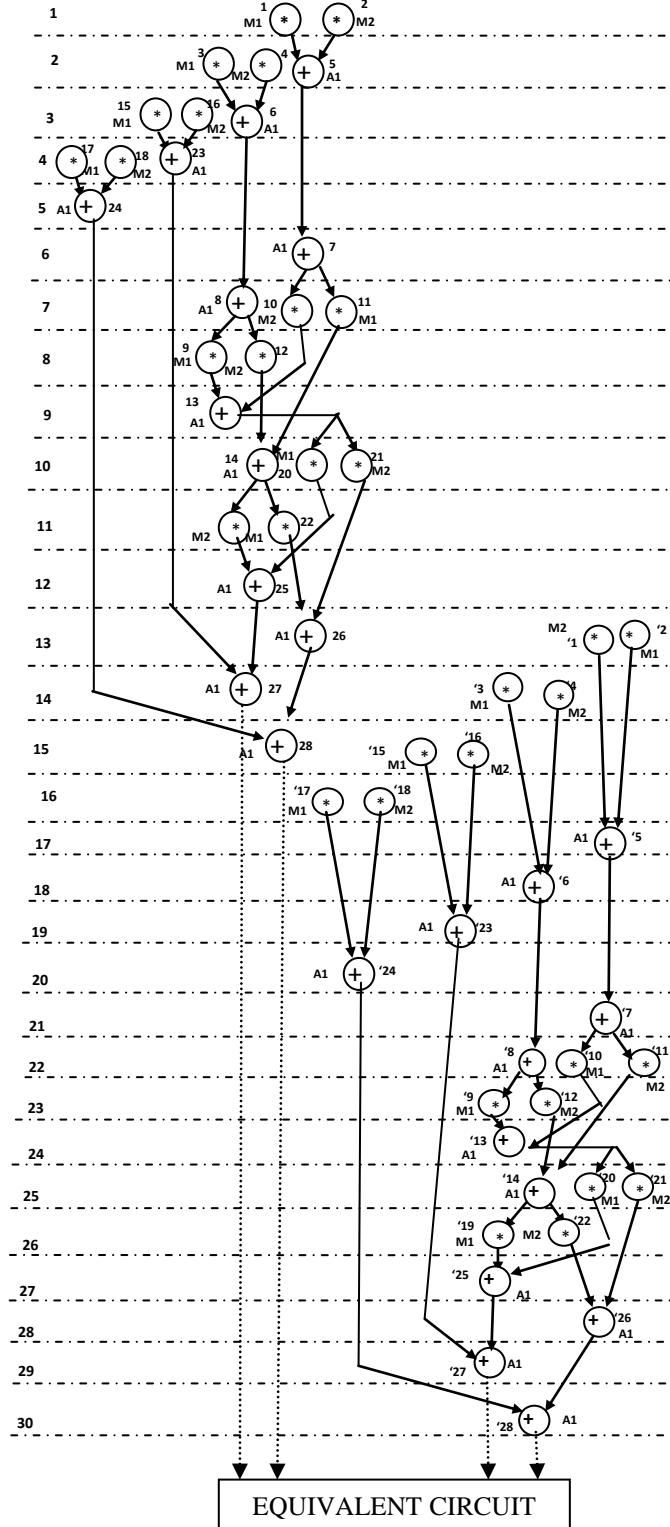

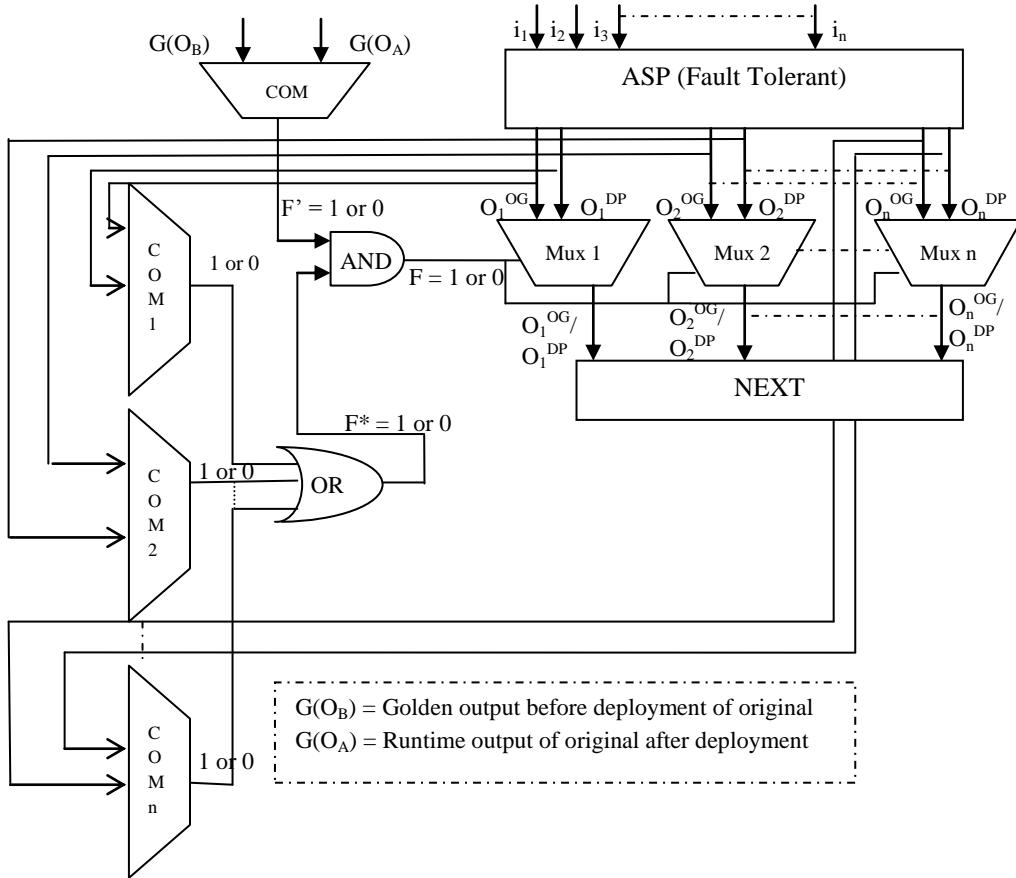

| Figure 6.6.  | Circuit Diagram for Voting Scheme                                                                                                                              | 66  |

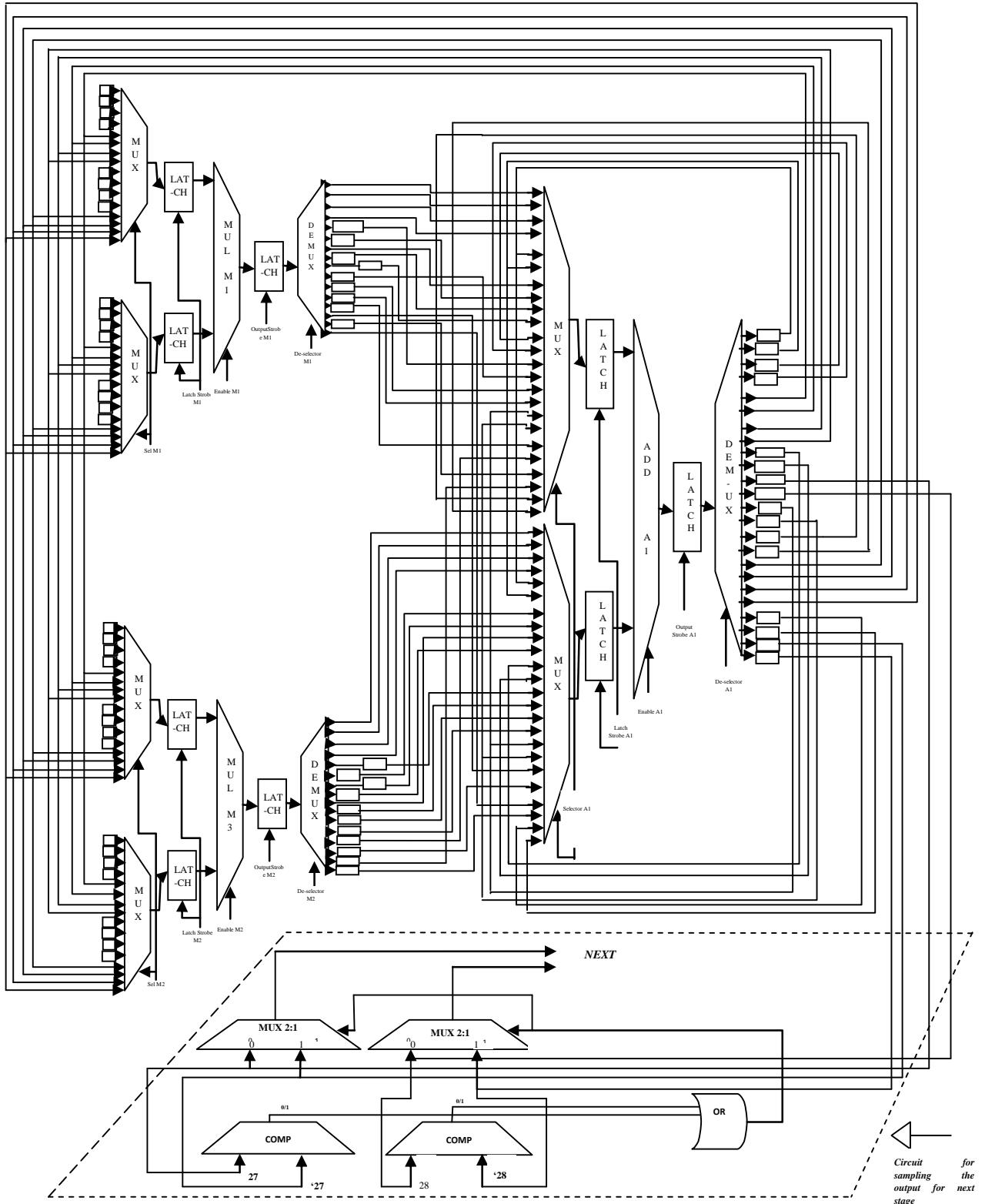

| Figure 6.7.  | Datapath Circuit Corresponding ARF with $X_i = 1(+), 2(*)$                                                                                                     | 68  |

| Figure. 6.8  | SDFG <sup>TMR</sup> for [32] Corresponding ARF with $X_i = 5(+), 6(*)$ for $k_c = 2$                                                                           | 70  |

| Figure 7.1   | An Infected 1- bit Adder IP Present in Module Library of a HLS Tool                                                                                            | 73  |

| Figure 7.2   | Proposed Methodology for Trojan Secured Datapath                                                                                                               | 74  |

| Figure 7.3   | IIR Filter for $A_v = 0$ ; $\vec{R}_n = 2(+), 5(*)$ indicating Alternate Assignment Procedure of Two Vendor Types                                              | 76  |

| Figure 7.4   | IIR Filter for $A_v = 1$ ; $\vec{R}_n = 2(+), 5(*)$ indicating Each Entire Unit Strictly Assigned to Same Vendor Type ( $U^{OG}$ to 'V1' and $U^{DP}$ to 'V2') | 76  |

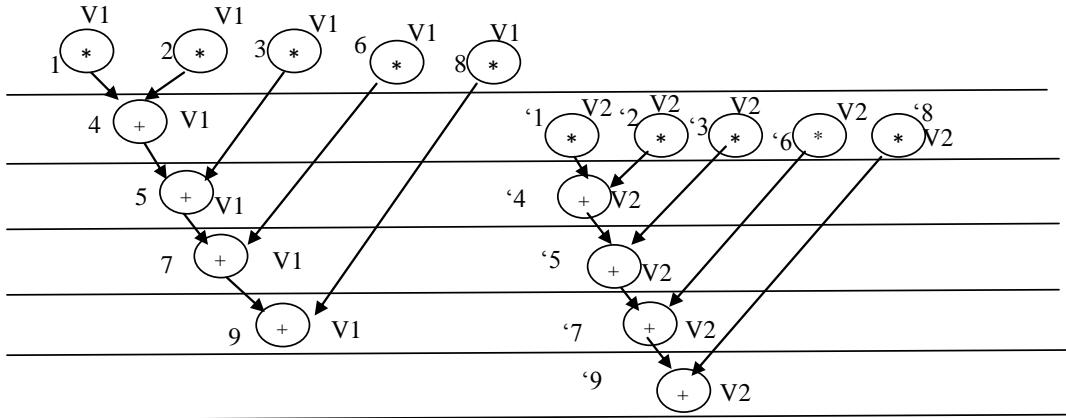

| Figure 8.1   | Comparison of Convergence Time with respect to Step Size $C(i)$                                                                                                | 83  |

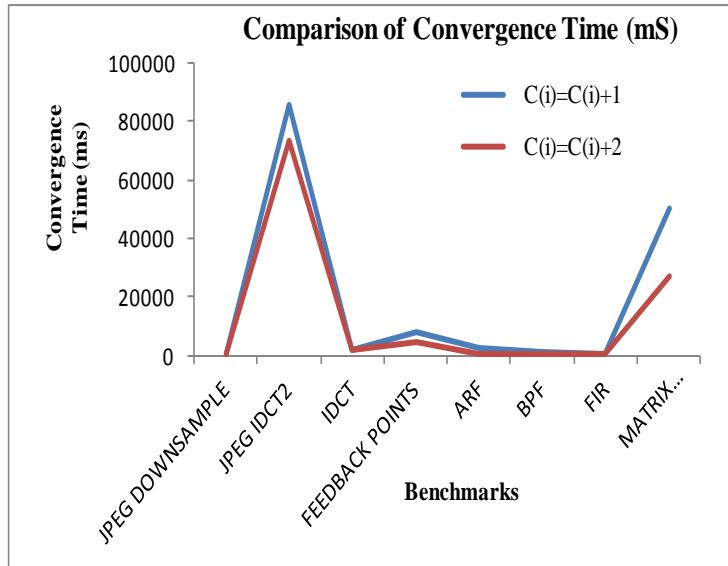

| Figure 8.2   | Comparison of Exploration Time with respect to Step Size $C(i)$                                                                                                | 85  |

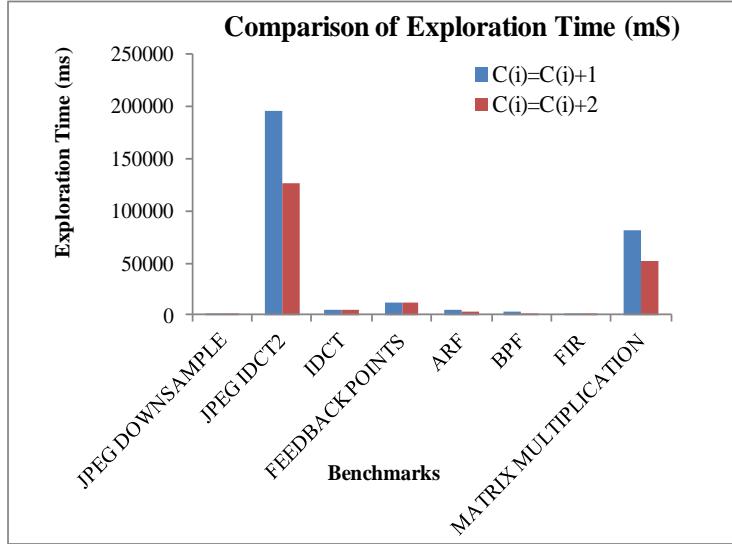

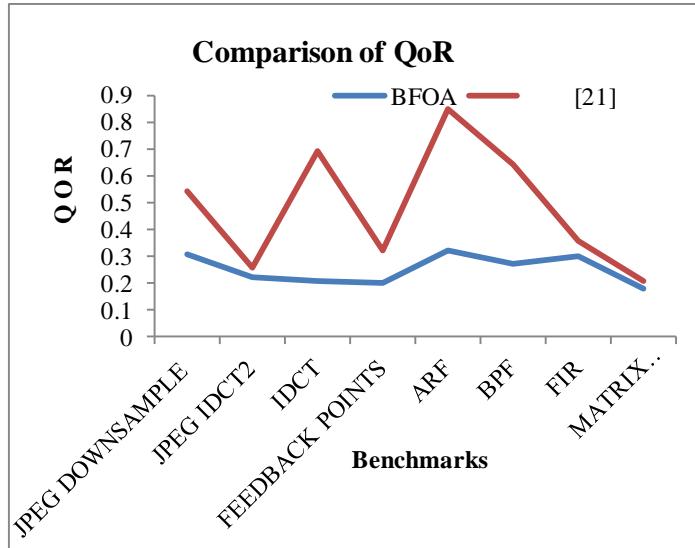

| Figure 8.3   | Comparison of QoR between BFOA-DSE and [20] Approach                                                                                                           | 87  |

| Figure 8.4   | Comparison of QoR between BFOA-DSE and [21] Approach                                                                                                           | 88  |

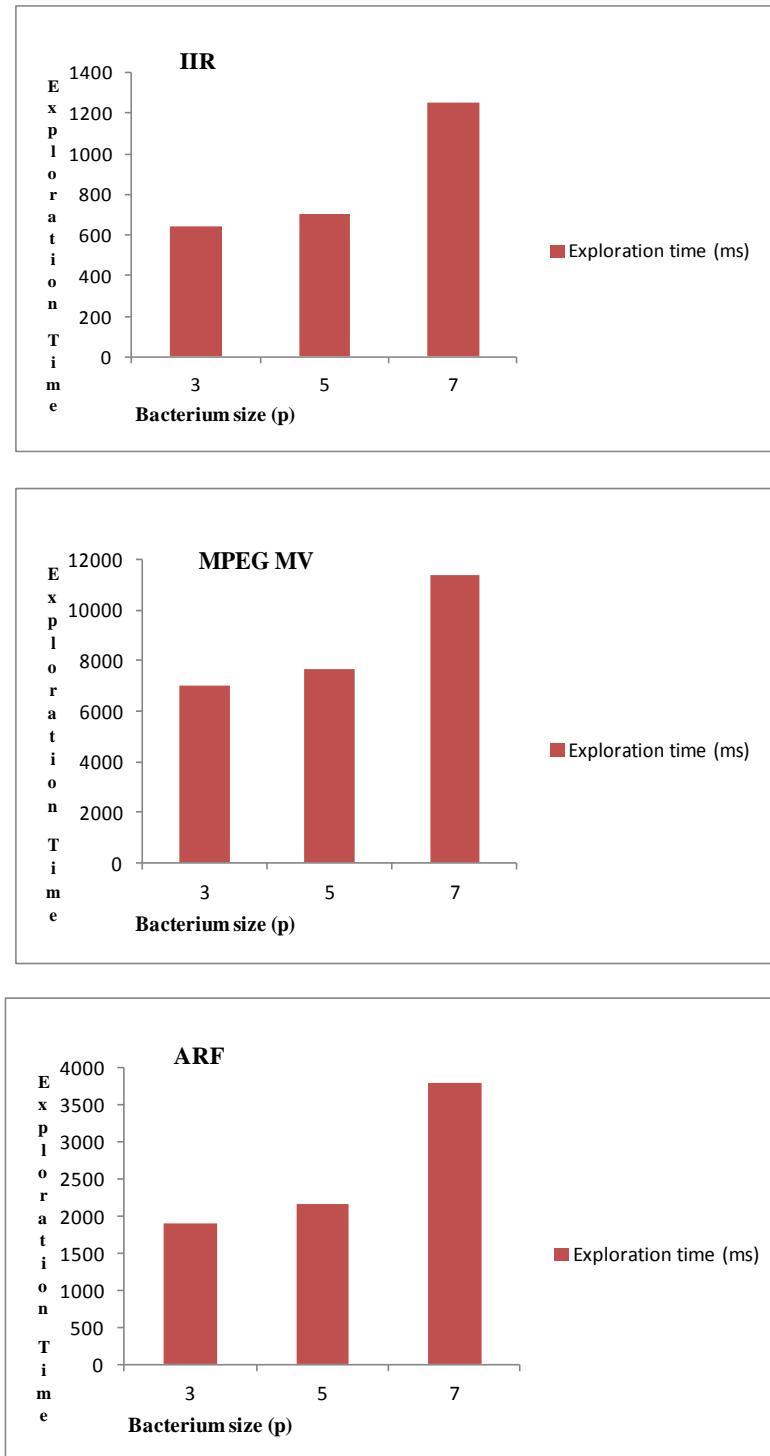

| Figure 8.5   | Graphical Representation of Variation of Exploration Time (in ms) with respect to Change in Bacterium size ( $p$ )                                             | 106 |

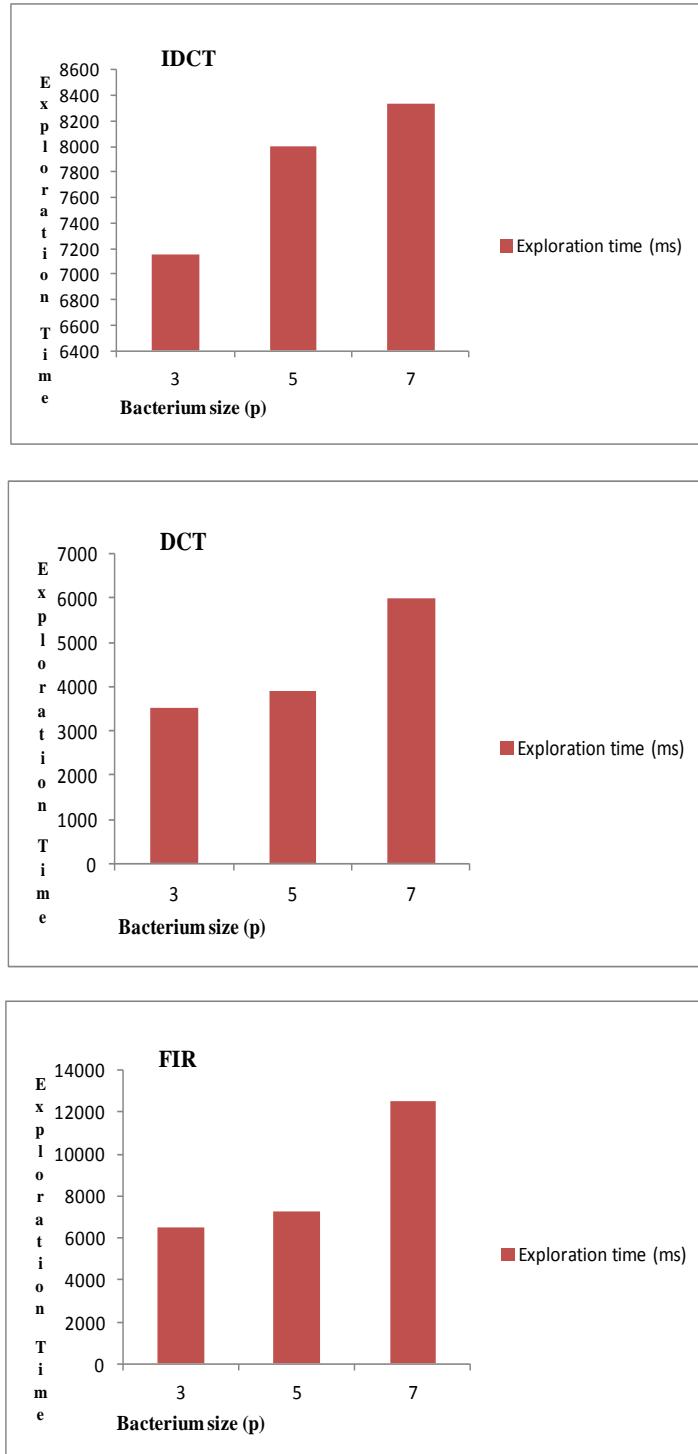

| Figure 8.6   | Graphical Representation of Variation of Exploration Time (in ms) with respect to Change in Bacterium size ( $p$ )                                             | 107 |

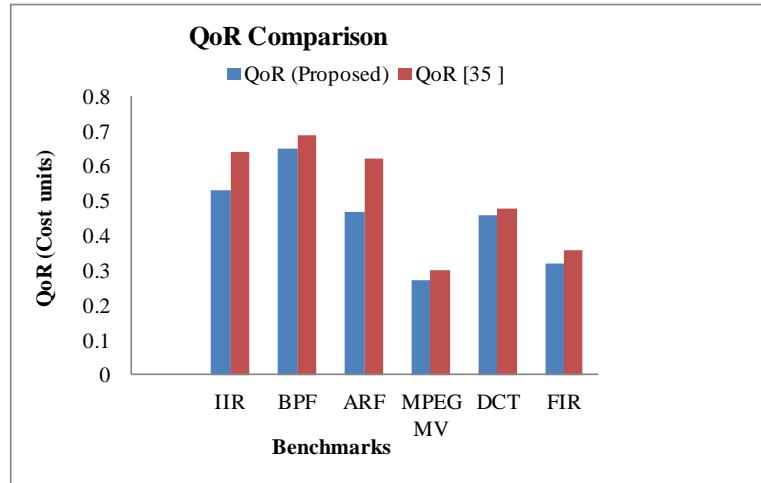

| Figure 8.7   | Comparison of QoR (cost units) of Proposed and [35] Approach                                                                                                   | 109 |

## LIST OF TABLES

|            |                                                                                                                                       |     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.1  | Module Library Used                                                                                                                   | 21  |

| Table 8.1  | Comparison of QoR and Exploration Time with respect to Bacterium size ( $p$ ) for the Proposed Approach                               | 82  |

| Table 8.2  | Impact in the Variation of Step Size ( $C(i)$ ) on the Performance of Proposed DSE                                                    | 83  |

| Table 8.3  | Results of Estimated Power and Execution Time using Proposed Approach for DFGs                                                        | 86  |

| Table 8.4  | Comparison Of Proposed Approach With [20] in Terms of Exploration Time and Cost                                                       | 86  |

| Table 8.5  | Comparison Of Proposed Approach With [21] in Terms of Exploration Time and Cost                                                       | 87  |

| Table 8.6  | Comparison Of Proposed DSE Approach With [20] and [21] in Terms of Quality Metrics and QoR                                            | 89  |

| Table 8.7  | Results of Proposed Fault Secure DSE approach for $k_c = 10$                                                                          | 92  |

| Table 8.8  | Comparison of Proposed Approach with Approach [28] and [30] for $k_c=1$                                                               | 92  |

| Table 8.9  | Variation of Exploration Time with Swarm Size ( $p$ ) in ms                                                                           | 94  |

| Table 8.10 | Exploration Time vs. Inertia Weight (at $p = 3$ )                                                                                     | 94  |

| Table 8.11 | Experimental Results of the Proposed Approach for $k_c = 1$                                                                           | 95  |

| Table 8.12 | Experimental Results of the Proposed Approach for $k_c = 4$                                                                           | 95  |

| Table 8.13 | Variation of Proposed Approach with [28]                                                                                              | 96  |

| Table 8.14 | Results of Proposed Fault Tolerant DSE Approach for $k_c = 1$                                                                         | 98  |

| Table 8.15 | Comparison of Proposed Approach with [32] in Terms of Resource (Hardware) Utilized for Fault Tolerant Datapath for ( $k_c = 1$ )      | 98  |

| Table 8.16 | Results of Proposed Fault Tolerant DSE Approach for $k_c = 2$                                                                         | 99  |

| Table 8.17 | Results of Proposed Fault Tolerant DSE Approach For $k_c = 3$                                                                         | 99  |

| Table 8.18 | Comparison of Proposed Approach with [32] in Terms of Resource (Hardware) Utilized for Fault Tolerant Datapath for ( $k_c = 2$ and 3) | 100 |

|            |                                                                                             |     |

|------------|---------------------------------------------------------------------------------------------|-----|

| Table 8.19 | Results of Proposed Approach (for $k_c = 1$ ) in Terms of Optimality                        | 100 |

| Table 8.20 | Results of Proposed Approach (for $k_c = 3$ ) in Terms of Optimality                        | 101 |

| Table 8.21 | Comparison of Proposed Approach with [32] Fault Tolerant Approach                           | 101 |

| Table 8.22 | Comparison of Proposed Approach with [32] Fault Tolerant Approach                           | 102 |

| Table 8.23 | Comparison of Proposed Approach with [28] Fault Secured Approach                            | 103 |

| Table 8.24 | Comparison of Exploration Time with respect to Bacterium size ‘ $p$ ’ for Proposed Approach | 105 |

| Table 8.25 | Results of Proposed Trojan Secured Approach                                                 | 108 |

| Table 8.26 | Comparison of Proposed Approach with [35]                                                   | 108 |

## NOMENCLATURE

|                  |                                                                             |

|------------------|-----------------------------------------------------------------------------|

| $p$              | Population Size                                                             |

| $D$              | Total number of resource types                                              |

| $R_x$            | Candidate resource combination for optimal solution                         |

| $X_i$            | Resource combination                                                        |

| $X_i^{Last}$     | Last resource set of $i^{\text{th}}$ bacterium solution                     |

| $X_i^{New}$      | New configuration of the particle/bacterium                                 |

| $P_T$            | Power consumed by a resource configuration                                  |

| $P_S$            | Static power consumed by a resource configuration                           |

| $P_D$            | Dynamic power consumed by a resource configuration                          |

| $P_{cons}$       | Power constraints specified by the user                                     |

| $P_{\max}$       | Maximum power consumed by a resource configuration in design space          |

| $P_{\min}$       | Minimum power consumed by a resource configuration in design space          |

| $P_T^{DMR}$      | Power consumed by a fault secured DMR system                                |

| $P_S^{DMR}$      | Static power consumed by a fault secured DMR system                         |

| $P_D^{DMR}$      | Dynamic power consumed by a fault secured DMR system                        |

| $P_{\max}^{DMR}$ | Maximum power consumed by a fault secured DMR system                        |

| $P_{\min}^{DMR}$ | Minimum power consumed by a fault secured DMR system                        |

| $p_c$            | Power dissipated per area unit (e.g. transistors)                           |

| $A_{cons}$       | Area constraints specified by the user                                      |

| $A_T^{DMR}$      | Area consumed by a fault secured DMR system                                 |

| $A_{\max}^{DMR}$ | Maximum area consumed by a fault secured DMR system                         |

| $L$              | Latency of a resource configuration                                         |

| $T_c$            | Initiation interval or cycle time of a resource configuration               |

| $T_E$            | Execution time consumed by a resource configuration                         |

| $T_{cons}$       | Execution time constraints specified by the user                            |

| $T_{\max}$       | Maximum execution time consumed by a resource configuration in design space |

| $T_{\min}$       | Minimum execution time consumed by a resource configuration in design space |

| $T_E^{DMR}$      | Execution time consumed by a fault secured DMR system                       |

|                                         |                                                                         |

|-----------------------------------------|-------------------------------------------------------------------------|

| $T_{\max}^{DMR}$                        | Maximum execution time consumed by a fault secured DMR system           |

| $T_{\min}^{DMR}$                        | Minimum execution time consumed by a fault secured DMR system           |

| $K(R_d)$                                | Represents the area occupied by resource $R_d$                          |

| $N(R_d)$                                | number of instances of resource type $R_d$                              |

| $N(R_d)^{New}$                          | New value of the $d^{\text{th}}$ resource type                          |

| $N(R_d)^{\max}$                         | Maximum value of $d^{\text{th}}$ resource type                          |

| $N(R_d)^{\min}$                         | Minimum value of $d^{\text{th}}$ resource type                          |

| $t_{\min}$                              | Minimum temperature                                                     |

| $t_{\max}$                              | Maximum temperature                                                     |

| $Temp$                                  | Initial temperature of exploration process                              |

| $\Delta t$                              | $T_w / N_c$                                                             |

| $T_w$                                   | Temperature window                                                      |

| $j$                                     | Current iteration step/chemotactic step                                 |

| $k$                                     | Replication steps counter                                               |

| $l$                                     | Elimination dispersal step counter                                      |

| $N_c$                                   | Maximum number of chemotactic steps                                     |

| $N_{\text{re}}$                         | Maximum number of replication steps                                     |

| $N_{\text{ed}}$                         | Maximum number of elimination dispersal steps                           |

| $\Delta(i)$                             | Tumble Vector                                                           |

| $C(i)$                                  | Step size                                                               |

| $C(i)^{New}$                            | New step size generated                                                 |

| $C(i)^{Last}$                           | Last step size used                                                     |

| $\text{Rep}[j-])$                       | Array to check whether replication performed or not                     |

| $\text{Ed}[j-])$                        | Array to check whether elimination dispersal performed or not           |

| $x$                                     | Step # at which replication has to be performed                         |

| $y$                                     | Step # at which elimination dispersal has to be performed               |

| $C_f(X_i)$                              | Cost of bacterium with resource set $X_i$ fitness of particle/bacterium |

| $C_{f_{ibi}}(X_i)$                      | Local best fitness of particle ' $X_i$ '                                |

| $E_{FU}$                                | Energy consumed by the major FU's                                       |

| $E_{\text{mux}}$ and $E_{\text{demux}}$ | Energy consumed by the multiplexers and de-multiplexers                 |

| $\phi_1$ and $\phi_2$                   | User defined weights                                                    |

| $k_c$                                   | strength of the fault                                                   |

|                   |                                                                             |

|-------------------|-----------------------------------------------------------------------------|

| $Z$               | Termination criteria                                                        |

| $U^{OG}$          | Original unit                                                               |

| $U^{DP}$          | Duplicate unit                                                              |

| $c.s$             | Control steps                                                               |

| $X_{gb}$          | Global best position                                                        |

| $X_{lbi}$         | Local best position for an $i^{th}$ particle                                |

| $P_m$             | Mutation Probability                                                        |

| $R_{d_i}^+$       | New resource value of particle $X_i$ in $d^{th}$ dimension                  |

| $R_{d_i}$         | Previous resource value of particle $X_i$ in $d^{th}$ dimension             |

| $R_{dlbi}$        | Resource value of $X_{lbi}$ in $d^{th}$ dimension                           |

| $R_{dgb}$         | Resource value of $X_{gb}$ in $d^{th}$ dimension                            |

| $V_{d_i}^+$       | New velocity of particle $X_i$ in $d^{th}$ dimension                        |

| $UF$              | Unrolling factor                                                            |

| $UF_N$            | $N^{th}$ unrolling factor                                                   |

| $C_{body}^{DMR}$  | Number of CS required to execute loop body of CDFG <sup>DMR</sup>           |

| $C_{first}^{DMR}$ | Number of CS required to execute first iteration of the CDFG <sup>DMR</sup> |

| $I$               | Maximum number of iteration (loop count)                                    |

| $\Delta$          | Delay of one CS in nanoseconds                                              |

| $\mathfrak{L}$    | Number of iteration                                                         |

| $D_c$             | Dependency information                                                      |

| $D(opn)$          | Delay of operation ‘ $n$ ’                                                  |

| $A_v$             | Vendor allocation procedure type                                            |

## ACRONYMS

|       |                                           |

|-------|-------------------------------------------|

| IC    | Integrated Circuits                       |

| VLSI  | Very Large Scale Integration              |

| HLS   | High Level Synthesis                      |

| HDL   | Hardware Description Languages            |

| DFG   | Data Flow Graph                           |

| RTL   | Register Transfer Level                   |

| CDFG  | Control Data Flow Graph                   |

| DSE   | Design Space Exploration                  |

| ASAP  | As Soon As Possible                       |

| ALAP  | As Late As Possible                       |

| FU    | Functional Units                          |

| GA    | Genetic Algorithm                         |

| WSPSO | Weighted Sum Particle Swarm Optimization  |

| CED   | Concurrent Error Detection                |

| TMR   | Triple Modular Redundant                  |

| SET   | Single Event Transient                    |

| SoC   | System-On-Chip                            |

| IP    | Intellectual Property                     |

| 3PIP  | Third Party Intellectual Property         |

| DMR   | Double Modular Redundant                  |

| BFOA  | Bacterial Foraging Optimization Algorithm |

| QoR   | Quality Of Result                         |

| ED    | Elimination-Dispersal                     |

| PSO   | Particle Swarm Optimization               |

| SEU   | Single Event Upset                        |

| SDFG  | Scheduled Data Flow Graph                 |

| EA    | Evolutionary Algorithm                    |

|        |                                          |

|--------|------------------------------------------|

| TFH    | Transient Fault Hazards                  |

| LET    | Linear Energy Transfer                   |

| MCFT   | Multi Cycle Fault Tolerance              |

| VHDL   | VHSIC Hardware Description Language      |

| FPGA   | Field Programmable Gate Array            |

| ARF    | Auto Regressive Filter                   |

| BPF    | Band Pass Filter                         |

| DCT    | Discrete Cosine Transformation           |

| IDCT   | Inverse Discrete Cosine Transformation   |

| DWT    | Discrete Wavelet Transform               |

| FIR    | Finite Impulse Response                  |

| WDF    | Wave Digital Filter                      |

| EWF    | Elliptic Wave Filter                     |

| FFT    | Fast Fourier Transformation              |

| MO-DSE | Multi Objective Design Space Exploration |

# Chapter 1

## Introduction

### 1.1 Preamble

With the explosion of technology, the 20<sup>th</sup> century era witnessed a drastic change in the lifestyle. The key inventions on Integrated Circuits (ICs) have led to high speed microprocessors and memories. With the advent of such breakthroughs, there have been equally important developments which have brought steady growth in digital systems. In early 60s, *Moore*, predicted the exponential growth of the number of transistors on an integrated circuit. This in turn provided higher functionalities within a single unit at low cost, leading to higher complexity while designing and verification.

As the complexity of systems increases, there arises need for automation at higher abstraction levels where functionalities and tradeoffs are easier to understand. Automation assures a shorter design cycle. Also, there is a greater possibility of quickly exploring different and better designs. Raising the design abstraction to behavioural level or architectural level boosts the design productivity [1, 60, 61, 62]. An architectural level specification describes the algorithm to be implemented, without the details of the structure of the circuit.

### 1.2 Circuit Design and Synthesis

The Very Large Scale Integration (VLSI) design flow consists of a number of design and test levels to match the design specifications. The design engineer accepts the user requirements, and translates them into specifications. Once the specifications are determined, the designing is performed. The process includes system level, high level, gate or logic level, transistor or circuit level and physical or layout level. The levels can be described as [1]:

- *System level*: This is the highest level of abstraction, where the system is represented as processes, tasks, hardware and software. This level deals with the overall system and the information flow within the system.

- *Behavioural or Algorithmic or High level*: This level controls the computation by individual processors within the system. It monitors the mapping sequences of inputs to the outputs.

- *Register Transfer Level (RTL)*: At this level, the system is specified as a set of storage elements and functional units.

- *Logic or Gate level*: At the logic level system is viewed as a network of gates and flip-flops. The behaviour of the system is specified in terms of logic equations.

- *Circuit or Transistor level*: this level describes the circuits as a netlist of transistors. The issues related to the nature and numbers of transistors to be used are dealt at the circuit level.

- *Physical or Layout level*: This is the lowest level of circuit abstraction in which the system is specified in terms of individual transistors.

The design process proceeds from higher to lower abstraction levels. The automated process of designing the VLSI circuits is referred as synthesis. Specifying the design at a higher abstraction level has been an effective way to deal with the complexity.

### 1.3 High Level Synthesis (HLS) Details

With the increasing design complexity of ICs the idea of automatically generating circuit implementations from high-level behavioural specifications has gained interest. Initially, multiple prototype tools were developed to call attention to the methodology and to experiment with various algorithms. In late 80s and early 90s, a number of similar HLS tools were built, mostly for research and prototyping. MIMOLA [2], ADAM [3, 4], HAL [5], Hercules/Hebe [7, 8], and Hyper/Hyper-LP [6, 9] were some academic efforts. These tools decompose the synthesis task into following steps:

- a) Code transformation,

- b) Module selection,

- c) Operation scheduling,

- d) Datapath allocation, and

- e) Controller generation.

These problems were individually addressed later using algorithms like list scheduling algorithm, force-directed scheduling algorithm and many others. This provided a base for HLS. However, these efforts were not enough for wide acceptance of HLS among designers due to low quality solutions generated.

```

r = a+b;

s = c*d;

t = e*f;

u = r+s;

v = u +t

```

**Figure 1.1** Sample Behavioural description

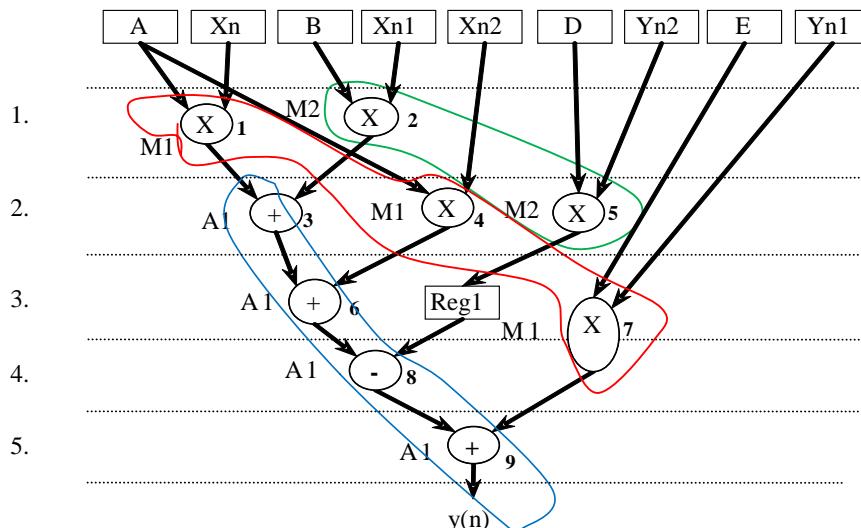

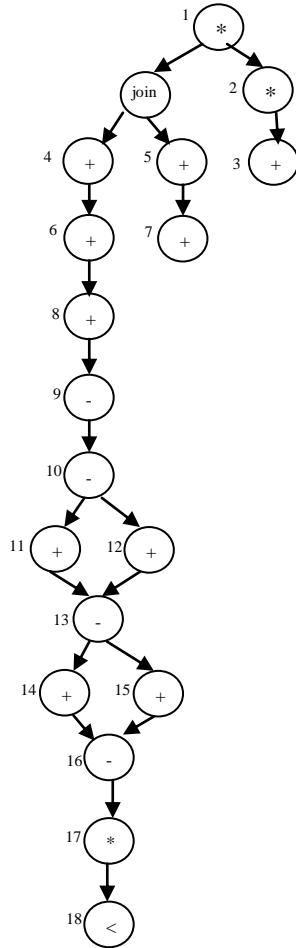

**Figure 1.2** Sample Data Flow Graph

In 1995 several tools like Behavioural Compiler [11] from Synopsis, Monet from Mentor Graphics [10] and Visual Architect from Cadence [12] were introduced which received a wide attention. However, the tools were not widely accepted since these tools used Hardware Description Languages (HDL) such as Very High Speed Integrated Circuit Hardware Description Language (VHDL) or Verilog for behavioural description as input. Since then a wide range of tools are developed which are commercially accepted and use C/C++ or C-based languages to capture the design.

#### 1.4 Theoretical Background on HLS

HLS is a process of transforming a software behavioural description into a hardware circuit description with equivalent functionality [60-63]. It is sometimes referred as behavioural or architectural or C-to-gates synthesis. The behavioural description describes the input and output behaviour of the algorithm in terms of operations and data transfers. It consists of algorithmic statements containing the different operations viz. additions, multiplications, logical operations and control operations like loops, conditional statements and function calls. The behavioural description is represented in the form of a Data Flow graph (DFG). The DFG comprises of operations in the algorithmic description and the data dependencies between them are represented by the vertices and edges, respectively. Figure 1.2 gives an example of a sample DFG for the behavioural description shown in Figure 1.1. The hardware circuit description is divided into segments, datapath unit and control unit. The datapath includes the functional units such as multipliers, arithmetic logical units, and the storage units while the control unit coordinates the data flow between the datapath elements. Traditionally HLS is divided into datapath synthesis and controller synthesis. Datapath synthesis can be modelled as the process of searching a complex multidimensional space represented by the

set of possible schedules, allocations, and bindings that can realize a given behavioural specification.

## 1.5 Phases of HLS

The various phases or tasks of HLS include compilation, transformation, scheduling, allocation, binding and RTL generation. During compilation the behavior of the system specified in the form of an algorithmic description or HDL (VHDL or Verilog) is compiled into internal representations. These internal representations are generally in the form of a DFG or a Control Data Flow Graphs (CDFG). Further in the transformation phase, the generated DFG is transformed into an optimized DFG or a suitable DFG for scheduling and allocation purpose. Dead-code elimination, common subexpression elimination, loop unrolling, constant propagation and code motion are some possible transformations which can be done on an application. Once the transformations are done, the Design Space Exploration (DSE) process is performed. During DSE several choices have to be evaluated for executing any decision. Therefore, it is important to perform DSE at early design stage or higher abstraction level (behavioural level) in order to investigate tradeoffs between all possible design goals, and to select the most appropriate solution. Finally, to realize a RTL design, HLS performs scheduling, allocation and binding. Scheduling divides the algorithmic behaviour/DFG into control steps. Each step contains a small section of code that can be executed in a single clock cycle. This process optimizes the number of execution steps based on constraints of hardware resource and cycle time. Allocation decides how much resources are needed in hardware while binding map the instructions and variables to hardware components, such as adders, multipliers, and registers [64]. The scheduling, allocation and binding phases are described in detail in next sections.

- *Scheduling*

The scheduling is a process which maps operations belonging to the algorithmic description onto a set of discrete time steps, in a way such that all data dependencies/precedence constraints specified in the algorithmic description are met. The mapping of operations to time steps is done such that the total number of time steps required to implement the specified behaviour meets the given timing constraints and minimizes implementation area. Scheduling can either be constructive or iterative [1, 66, 67, 69].

In constructive scheduling the solutions are constructed by adding operations/nodes one at a time until all the operations have been scheduled. As Soon As Possible (ASAP), As Late As

Possible (ALAP), List scheduling [13], Force direct scheduling [14], and Integer linear programming based scheduling [15, 16] fall under constructive category. ASAP is the simplest type of scheduling. It assumes that the number of Functional Units (FU's) required are already specified. Further, process arranges the operations topologically according to their data or control flow. Once the operations are sorted, they are selected one by one from the list in order and scheduled into earliest control step possible, preserving its dependency and the resource availability. However, another constructive scheduling approach, ALAP, places the operations in the latest possible control step. ALAP uses the number of steps resulting from the ASAP schedule as a latency constraint [1]. ASAP, ALAP are also referred as the unconstrained scheduling algorithms. List scheduling is primarily resource-constrained scheduling algorithm. The list-based algorithm takes a sequencing DFG and resource constraints as inputs and generates a scheduled sequencing DFG as output. The operations available for scheduling are kept in a list for each control step. This list is further ordered by some priority function, either mobility of the vertex or the length of path from the operation to the sink while ranking the vertices in decreasing order. An operation on the list is scheduled one by one if the resource needed by the operation is free; otherwise, it is deferred to the next clock cycle. Further, a Force-directed scheduling is a heuristic algorithm that can consider both resource and time constraints. The basic idea of this algorithm is to balance the concurrency of operations without increasing the total execution time to maximize the utilization of resources such that the number of required resources is minimal [1].

However, in iterative scheduling the designer starts with an initial (random) solution and iteratively updates the solution. Finally a scheduling solution is generated which is optimal and satisfies the user constraints of power/area and latency. In iterative scheduling the designer possesses multiple designing solutions which are generated in intermediate steps. Genetic Algorithm (GA) based scheduling, ant colony based scheduling, simulated annealing based scheduling are some examples of iterative approaches [65, 68, 70].

- *Allocation and Binding*

Allocation involves mapping operations onto functional units, assigning values to registers, and providing interconnections between operators and registers using buses and multiplexers. While binding is the task to assign operation to particular resource such as computation to functional unit, storage to register and data transfer to interconnect. **Binding can be solved by using various graph theoretic techniques like clique partitioning [1, 13, 71], circular-arc graph colouring [1, 13, 71] or left edge algorithm [1, 13].** In clique partitioning, an undirected graph

referred as “compatibility graph” is constructed to analyze the compatibility between the operations of the graph. Two operations are compatible and can use same resources if they need resources of same type and are scheduled in different clock cycles.

However, in graph colouring a resource conflict graph is constructed to analyze the conflicts of the operations, wherein, the graph is an undirected graph whose vertex set is in one-to-one correspondence with the operations and whose edge set denotes the conflicting vertex pairs. In such a resource conflict graph, two operations have a conflict if they are not compatible. The conflict graph and compatibility graph are complementary to each other. The choice between them is driven by the type of circuit.

Furthermore, in the left edge algorithm [1, 13], the birth time of a variable is mapped to the left edge, and the death time of a variable is mapped to the right edge. The variables are sorted in increasing order of their birth time. The first variable is then assigned to the first register. Then, the current register receives the next variable whose birth time is larger or equal to the death time of the previous variable.

## 1.6 Why HLS?

There has been an increase in trend towards automating synthesis at higher levels of designing in the recent years. Also, there has been substantial interest shown in RTL design obtained from higher levels of abstraction (algorithmic) using HLS. There are a number of reasons for this [1, 63, 65]:

- *Shorter design cycle*: Automation has reduced the designing time and manpower involvement metrics. Hence there is a reduction in the overall cost of the chip.

- *Continuous and reliable design flow*: HLS facilitates a continuous and reliable automatic translation of high level specification into RTL description of the circuit in the form of VHDL or Verilog.

- *Fewer errors*: Correct design decisions at the higher levels of circuit abstraction can ensure that the errors are not propagated to the lower levels.

- *The ability to search the design space*: Automating the design process helps in producing several designs for same specification in a reasonable amount of time. This benefit helps the designer in exploring different trade-offs between cost, speed, power and other factors to take an existing design and produce a functionally equivalent one that is efficient.

- *Easy availability of IC technology:* As more design expertise is moved into the synthesis system, it becomes easier for a non-expert to produce a chip that meets a given set of specifications.

## 1.7 Thesis Organization

The rest of the thesis is organized as follows: chapter 3 describes the proposed framework to solve the problem of DSE during power-performance trade-off for data intensive applications. Chapter 4 describes a framework to solve the problem of exploration of low cost optimal  $k$ -cycle transient fault secured datapath during power-performance trade-off for data intensive applications. Chapter 5 solves the problem of exploration of low cost optimal  $k$ -cycle transient fault secured datapath during area-delay trade-off for control intensive applications. In chapter 6, a framework to solve the problem of exploration of low cost optimal  $k$ -cycle transient fault tolerant datapath based on power-performance tradeoff for data intensive applications is presented. Moreover, chapter 7 solves the problem of exploration of low cost optimal Trojan secured datapath during behavioural synthesis for data intensive applications. Further, the results of the proposed approaches in context to the problems, for various well known HLS benchmarks indicating exploration time and quality improvements obtained, compared to the current existing approaches are provided in chapter 8. Chapter 9 concludes the research work presented in the thesis and provides future scope of work in this area.

# Chapter 2

## Previous Work and Thesis Contribution

### 2.1 Related Work

The problem of DSE in HLS is a NP-complete problem [72, 73, 74]. In the literature, many attempts have been made to solve the DSE problem in HLS [79-83]. The approaches developed; aim at exploring the design space along with balancing multi-conflicting issues during generation of the optimal/near-optimal design alternative (or Pareto front). For solving various NP complete problems, GAs is the most popular evolutionary algorithms in terms of diversity of their applications. In order to solve DSE problem, GA is used by many researchers in [18, 20, 21, 65, 66]. For example, researchers in [18] used a time constrained scheduling based on GA. In [18], authors combined the constructive scheduling methods with GA and later used for searching a suitable order to perform scheduling. The work presented an encoding scheme where allocation of supplementary resources was done during scheduling, to deal with the lower bound estimations. Authors in [20, 21, 65, 66] used GA to solve integrated scheduling and datapath exploration problem. In these approaches, the chromosome contains the scheduling information and the datapath information. In [20], the scheduling information is encoded with '*node priority*'. However, authors in [21], used the scheduling information in chromosome encoded by '*load factor*' and used a heuristic to decode the scheduling information from encoded chromosome. Authors in [65, 66] encoded scheduling information in chromosomes as '*work remaining*'. However, the second part of the chromosome in [20, 21, 65, 66] is encoded with maximum number of functional units available during scheduling. Furthermore, in [20] the cost function is evaluated on the basis on area-latency tradeoff. But, there is no concept of total execution time, data pipelining and power during exploration. Further, the chance of yielding an optimum result is not guaranteed. Researchers in [21] did not consider dynamic power while calculating total power. In the work, a multi-structure chromosome representation for the datapath nodes was used for scheduling. The approach also had a drawback of huge computation time besides

generating non-optimal solutions in some cases. Authors in [65, 66] used binary encoding of the chromosomes for DSE in architectural synthesis for area-latency trade-off. Moreover, authors in [65, 66], optimized area and latency, but failed to consider power and execution time (function of latency as well as cycle time for pipelined dataset), which are critical issues for modern handheld, battery operated high speed devices. In order to explore new solutions the approaches [18, 20, 21, 65, 66] perform genetic operator (such as crossover and mutation) between two chromosomes. In [19] a discrete Particle Swarm Optimization (PSO) based exploration method is proposed to solve the DSE problem in HLS. In the approach every swarm explores the design space by considering all conflicting objective simultaneously. The approach suffers from several drawbacks. The authors divided the swarm into sub-swarms and each objective was accomplished by one sub-swarm only. Hence, the technique required a large swarm size which may lead to heavy computation time per iteration. In the work, the authors have not considered the concept of local best while exploration. While updating velocity, the authors updated only the direction keeping the step length constant. Another drawback of the approach is that, there is no concept of mutation and clamping in case of boundary overreach problem.

Further in [17], authors described an approach based on integration of GA with PSO referred as Weighted Sum Particle Swarm Optimization (WSPSO). In [17] authors adopted the encoding scheme from [20], which is a combination of scheduling information and maximum available FUs. In their work, the concept of global and local best solution/position is used. To find new solutions, crossover is performed between current position with global best position and local best position. Thus, to incorporate GA, crossover is performed, which is the basic operator of GA and to incorporate PSO, the crossover is performed between current position and global and local best position. The shortcoming of this approach is that mathematically no velocity parameter is used while updating the particle position. Moreover, authors used a weighted combination of latency, area and power during fitness evaluation. But, the metrics such as execution time and actual power are not taken into account in cost function determination.

Besides these approaches, certain tools are introduced which deal with the DSE problem in HLS. In [22] a tool called SystemCoDesigner has been introduced which deals with tradeoff between area-delay. The tool offers automated and fast DSE with prototyping of behavioral systemC models. Some other commercial tools like GAUT [23], LegUp [24], ROCCC [25] and CatapultC [26] are also available in the market for electronic design automation. GAUT

takes a C/C++ behavioral description as input for automatically generating equivalent RTL implementation based on constraints of throughput and clock period. LegUp is an open source HLS tool available for FPGA-based processor/accelerator systems. Further, another tool called AutoPilot is introduced in [27] which address the problem of exploration in HLS. It performs C/C++/systemC-to-RTL synthesis. The tool was targeted for FPGAs.

The approaches mentioned so far suffered from multiple drawbacks and were not useful. Therefore, one of the objectives of this thesis is to develop an efficient DSE methodology in HLS which addresses the above drawbacks.

Over the years the process of DSE has evolved where the requirements specified by the user have also become more convoluted, ranging from simple area-delay tradeoff in initial years to complex power-delay-reliability tradeoff in recent years. To resolve this, some HLS approaches were proposed which included the consideration of fault security aspect with hardware redundancy, but without focusing on low cost solution of an optimized fault detectable design based on user power-delay constraint. The literature includes works that only deal with the fault detection issue of the designs without ability to explore a low cost optimized fault detectable datapath based on user specified power-delay. For example, HLS approaches such as [28, 29, 30, 31, 87] just included the aspect of single cycle fault security with hardware redundancy, but without any focus on evolving/exploring an optimal multi-cycle fault secured design based on user power-delay constraints. In [28] authors use duplication of the CDFG and map the second onto the same hardware as the first, adding FUs as needed. The technique uses the algebraic properties of associativity, distributivity, and commutativity to aid mobility in scheduling the duplicate CDFG and thus take better advantage of idle resources. The approach in [29] involves partitioning of the CDFG into regions or sub graphs. The authors presented a hardware redundancy based Concurrent Error Detection (CED) approach which breaks the data dependences between the nodes. This is done to improve the sharing between normal and duplicate computations. The original and the duplicate computations which are represented by a region are performed on distinct hardware. This is done so that, every regions output can be compared to identify the faults within the regions. For this, voting on the results of the regions is done. In [30], a CED scheme is employed to detect and isolate the faults within a system while it is in use. In [31] authors investigated a method for exploring the tradeoff between the area and latency of the CED design in HLS. The approach sometimes used hardware redundancy or time redundancy or a combination of both to produce fault secure designs. Designs were made secure on the

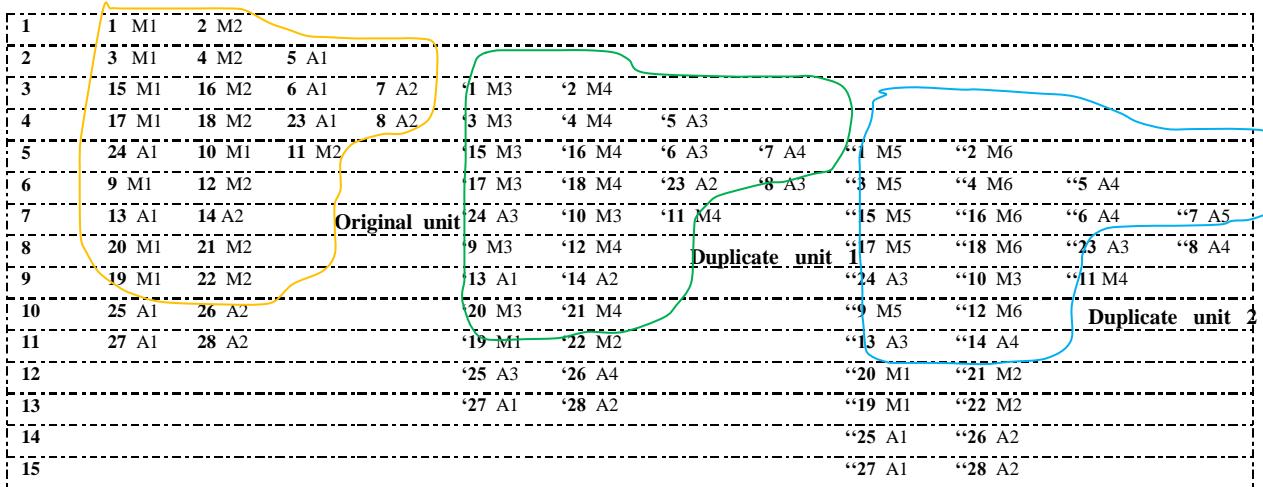

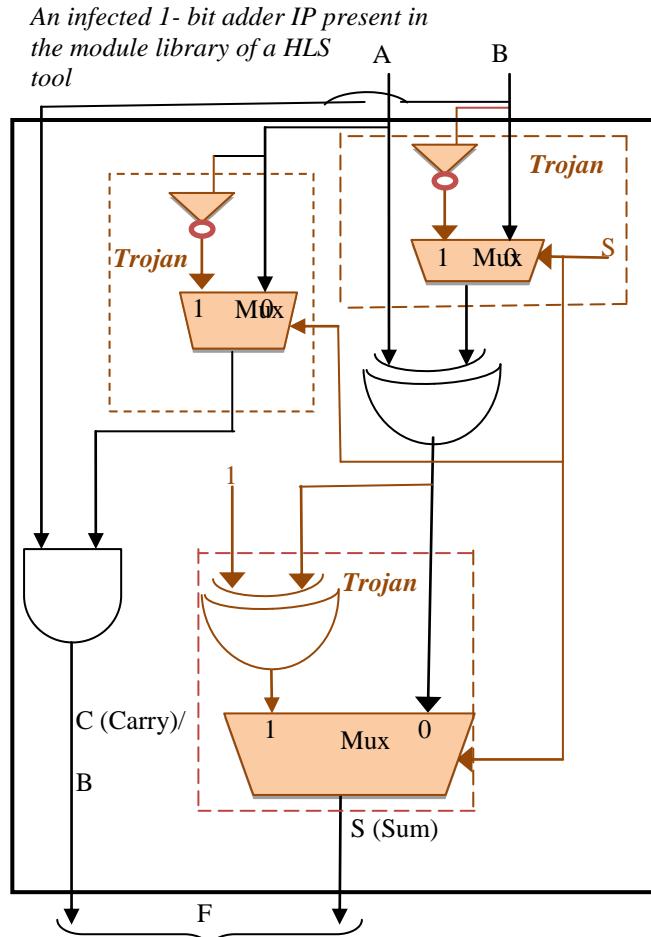

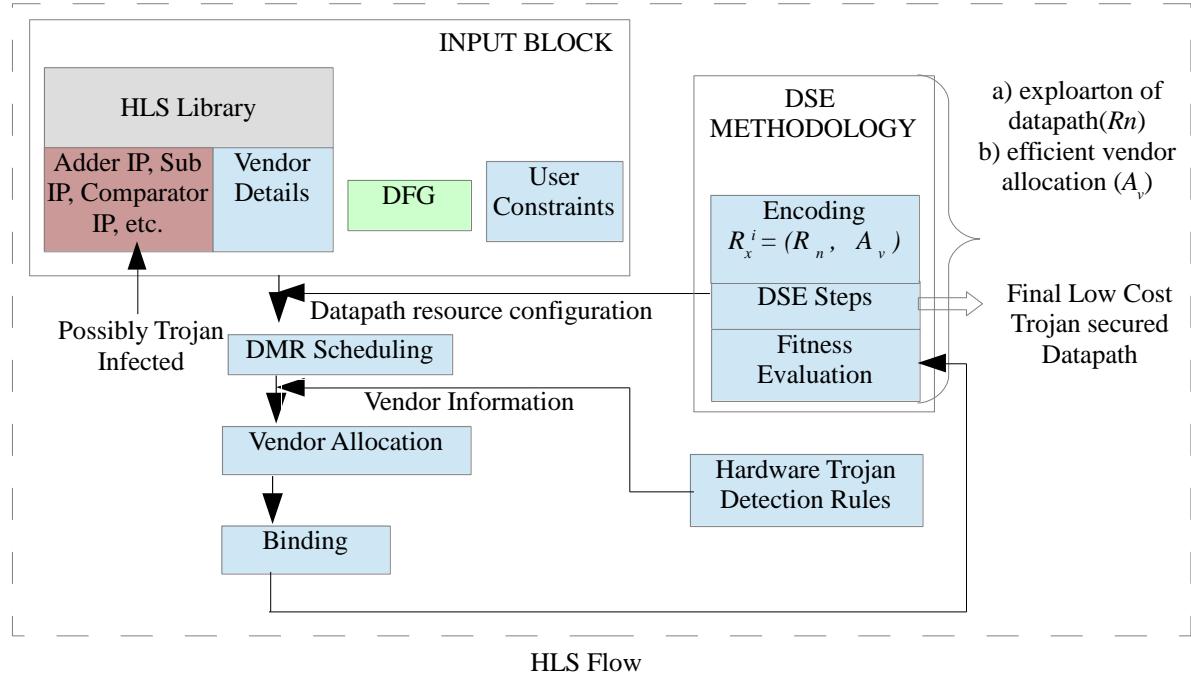

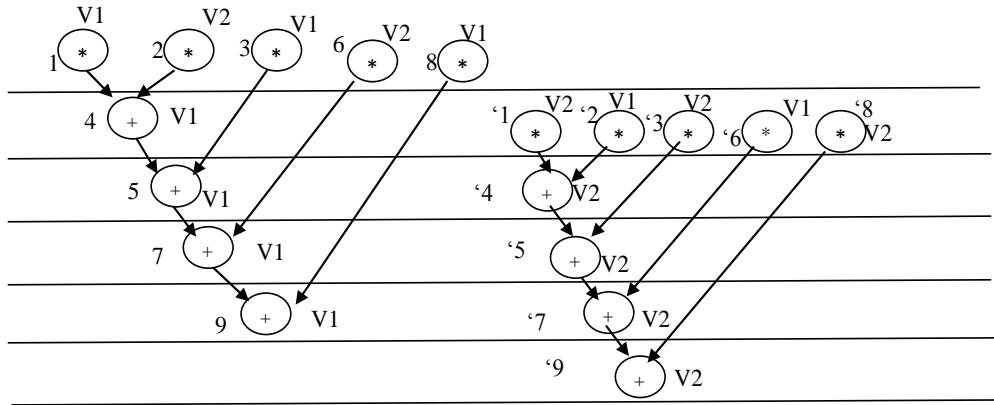

basis of check pointing introduced in the system. Instead of adding extra FUs for fault detection, they use re-computation on the same hardware using different allocations. Therefore approaches [28, 29, 30, 31] are all fault detectable approaches (using hardware redundancy) with no provision of producing an optimized fault detectable datapath system based on conflicting power and delay constraint of user.